# SGM61030 3A High Efficiency Synchronous Step-Down Converter

#### GENERAL DESCRIPTION

The SGM61030 is a high efficiency and miniature size synchronous step-down converter for low input voltage applications. This high frequency device does not need external compensation and is a perfect solution for compact designs. The 2.5V to 5.5V input voltage range is suitable for almost all available battery chemistries. For the SGM61030A version, to keep the high efficiency in the whole load range, the device operates in pulse width modulation (PWM) mode when the load is not light and automatically enters the power-save mode (PSM) at light loads. For the SGM61030B version, the device operates in continuous current mode (CCM) at light and heavy loads.

This device employs an adaptive off-time architecture, but still allows a wide range of output capacitors from  $22\mu F$  to  $150\mu F$  and even more. This flexibility makes the device a good choice for system power rails supplies. The adaptive off-time architecture provides excellent output voltage accuracy and superb load transient response.

The SGM61030 is available in a Green TDFN-2×2-7L package and can operate in the -40°C to +125°C ambient temperature range.

#### **FEATURES**

- 2.5V to 5.5V Input Voltage Range

- Adjustable Output Voltage from 0.6V to V<sub>IN</sub>

- Adaptive Off-Time Architecture

- Up to 95% Efficiency

- Low R<sub>DSON</sub> MOSFET Switches (43mΩ/24mΩ)

- 42µA (TYP) Operating Quiescent Current

- Ultra-Low Quiescent Current in Shutdown Mode

- Pulse-Skip Mode at Light Loads (SGM61030A)

- Continuous Current Mode (SGM61030B)

- 100% Duty Cycle Capability for Low Dropout

- Startup with Pre-biased Output

- Output Discharge Function

- Power Good Output

- Hiccup Mode Short-Circuit Protection

- Thermal Shutdown Protection

- Available in a Green TDFN-2×2-7L Package

#### **APPLICATIONS**

**Battery-Powered Applications**

Point-of-Load

**Processor Power Supplies**

Hard Disk Drives (HDD)/Solid State Drives (SSD)

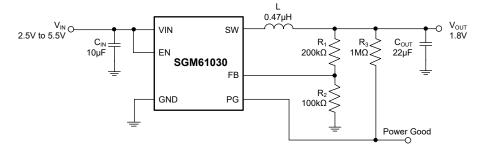

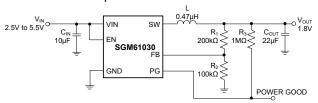

#### TYPICAL APPLICATION

Figure 1. SGM61030 Typical Application Circuit

#### PACKAGE/ORDERING INFORMATION

| MODEL     | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | MPERATURE ORDERING NUMBER |             | PACKING<br>OPTION   |  |

|-----------|------------------------|-----------------------------------|---------------------------|-------------|---------------------|--|

| SGM61030A | TDFN-2×2-7L            | -40°C to +125°C                   | SGM61030AXTEP7G/TR        | ORF<br>XXXX | Tape and Reel, 3000 |  |

| SGM61030B | TDFN-2×2-7L            | -40°C to +125°C                   | SGM61030BXTEP7G/TR        | G5N<br>XXXX | Tape and Reel, 3000 |  |

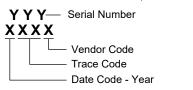

#### MARKING INFORMATION

NOTE: XXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

#### **ABSOLUTE MAXIMUM RATINGS**

| Pin Voltages Referred to GND            |                      |

|-----------------------------------------|----------------------|

| VIN, FB, EN, PG0.                       | 3V to 6V             |

| SW (DC)0.3V to V                        | <sub>IN</sub> + 0.3V |

| SW (AC, Less than 10ns) while Switching | 3V to 9V             |

| Package Thermal Resistance              |                      |

| TDFN-2×2-7L, θ <sub>JA</sub>            | 109°C/W              |

| Junction Temperature                    | +150°C               |

| Storage Temperature Range65°C to        | +150°C               |

| Lead Temperature (Soldering, 10s)       | +260°C               |

#### **RECOMMENDED OPERATING CONDITIONS**

| Input Voltage Range, V <sub>IN</sub>            | 2.5V to 5.5V            |

|-------------------------------------------------|-------------------------|

| Output Voltage Range, V <sub>OUT</sub>          | 0.6V to V <sub>IN</sub> |

| PG Pin Sink Current, ISINK_PG                   | 1mA                     |

| Maximum Pull-Up Voltage for PG, V <sub>PG</sub> | 5.5V                    |

| Operating Ambient Temperature Range             | 40°C to +125°C          |

| Operating Junction Temperature Range            | 40°C to +125°C          |

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

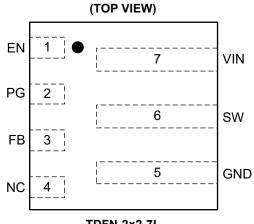

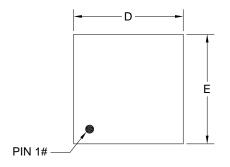

# **PIN CONFIGURATION**

TDFN-2×2-7L

## **PIN DESCRIPTION**

| PIN | NAME | I/O | DESCRIPTION                                                                                                                                                                                                                                                 |

|-----|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | EN   | I   | Active High Device Enable Input Pin. Pull this pin to logic high to enable the device and pull it low to disable it. An internal $550k\Omega$ (TYP) pull-down resistor disables the device by default. This resistor is removed when the device is enabled. |

| 2   | PG   | 0   | Open-Drain Power Good Output Pin. This output is released to go high if the device is in power good status. Pull up this pin to a 5.5V or less voltage rail. It can be left open if not used.                                                               |

| 3   | FB   | 1   | Feedback Pin. Connect a resistor divider between the output voltage sense point and ground and tap it to the FB pin to set the output voltage.                                                                                                              |

| 4   | NC   |     | No Connection. The pin can be connected to the ground or leave it floating.                                                                                                                                                                                 |

| 5   | GND  | G   | Ground Pin.                                                                                                                                                                                                                                                 |

| 6   | SW   | Р   | Switch Node of the Power Converter. Connect it to the output inductor.                                                                                                                                                                                      |

| 7   | VIN  | Р   | Input Voltage Pin.                                                                                                                                                                                                                                          |

NOTE: I = input, O = output, P = power, G = ground.

# **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 5V \text{ and } T_J = +25^{\circ}C, \text{ unless otherwise noted.})$

| PARAMETER SYMBOL                    |                     | CONDITIONS                                                                     | MIN | TYP                             | MAX | UNITS |

|-------------------------------------|---------------------|--------------------------------------------------------------------------------|-----|---------------------------------|-----|-------|

| Supply                              |                     |                                                                                |     |                                 |     |       |

| Input Voltage Range                 | V <sub>IN</sub>     |                                                                                | 2.5 |                                 | 5.5 | V     |

| Outline and Comment into VINI       |                     | Enabled, no load, no switching (SGM61030A)                                     |     | 42                              |     | μΑ    |

| Quiescent Current into VIN          | lα                  | Enabled, no load, no switching (SGM61030B)                                     |     | 550                             |     | μΑ    |

| Shutdown Current into VIN           | I <sub>SD</sub>     | Disabled (EN = Low)                                                            |     | 0.05                            |     | μΑ    |

| Under-Voltage Lockout Threshold     | \/                  | V <sub>IN</sub> falling                                                        |     | 2.2                             |     | V     |

| Under-Voltage Lockout Hysteresis    | V <sub>UVLO</sub>   | V <sub>IN</sub> rising                                                         |     | 200                             |     | mV    |

| Thermal Shutdown Threshold          | _                   | T <sub>J</sub> rising                                                          |     | 160                             |     | °C    |

| Thermal Shutdown Hysteresis         | - T <sub>JSD</sub>  | T <sub>J</sub> falling                                                         |     | 25                              |     | °C    |

| EN Input                            |                     |                                                                                |     |                                 |     |       |

| Logic High Input Voltage            | V <sub>IH</sub>     | V <sub>IN</sub> = 5V                                                           |     | 0.98                            |     | V     |

| Logic Low Input Voltage             | V <sub>IL</sub>     | V <sub>IN</sub> = 5V                                                           |     | 0.86                            |     | V     |

| Input Leakage Current (into EN Pin) | I <sub>EN_LKG</sub> | EN = High                                                                      |     | 0.03                            |     | μΑ    |

| Pull-Down Resistance at EN Pin      | R <sub>PD</sub>     | EN = Low                                                                       |     | 550                             |     | kΩ    |

| Soft-Start, Power Good              |                     |                                                                                |     |                                 |     |       |

| Soft-Start Time                     | t <sub>ss</sub>     | Time interval from EN rising edge to V <sub>OUT</sub> reaching 95% of nominal  |     | 0.8                             |     | ms    |

|                                     |                     | $V_{\text{OUT}}$ rising, as percentage of the nominal $V_{\text{OUT}}$         |     | 95% × V <sub>OUT</sub> (set)    |     | - V   |

| Power Good Threshold                | $V_{PG}$            | $V_{\text{OUT}}$ falling, as percentage of the nominal $V_{\text{OUT}}$        |     | 90% ×<br>V <sub>OUT</sub> (set) |     |       |

| PG Low State Output Voltage         | $V_{PG\_OL}$        | I <sub>SINK</sub> = 1mA                                                        |     | 0.15                            |     | V     |

| PG Leakage Current (into PG Pin)    | I <sub>PG_LKG</sub> | V <sub>PG</sub> = 5V                                                           |     | 0.02                            |     | μA    |

| Output and Feedback                 | •                   |                                                                                |     |                                 |     | •     |

| Feedback Regulation Voltage         | $V_{FB}$            | PWM mode, $2.5V \le V_{IN} \le 5.5V$ ,<br>$T_J = 0^{\circ}C$ to $+85^{\circ}C$ |     | 0.6                             |     | V     |

| Feedback Input Leakage Current      | I <sub>FB_LKG</sub> | V <sub>FB</sub> = 1V                                                           |     | 0.03                            |     | μA    |

| Output Discharge Resistor           | R <sub>DIS</sub>    | EN = Low, V <sub>OUT</sub> = 1.8V                                              |     | 43                              |     | Ω     |

| Power Switches                      | •                   |                                                                                |     |                                 |     |       |

| High-side MOSFET On-Resistance      | Б                   | I <sub>SW</sub> = 500mA                                                        |     | 43                              |     | mΩ    |

| Low-side MOSFET On-Resistance       | R <sub>DSON</sub>   | I <sub>SW</sub> = 500mA                                                        |     | 24                              |     | mΩ    |

| High-side MOSFET Current Limit      | I <sub>LIM</sub>    |                                                                                |     | 4.6                             |     | Α     |

| PWM Switching Frequency             | f <sub>SW</sub>     | I <sub>OUT</sub> = 1A                                                          |     | 2.5                             |     | MHz   |

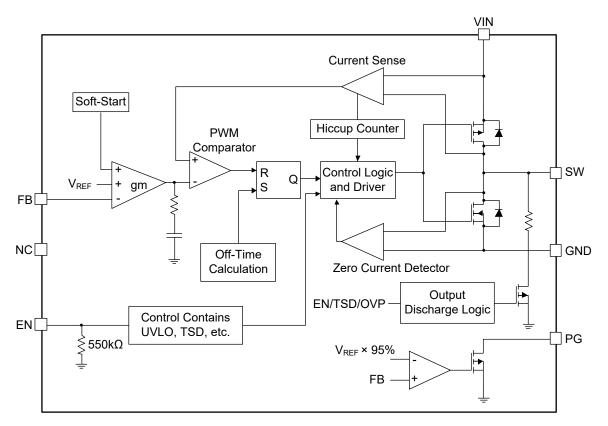

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. SGM61030 Block Diagram

#### DETAILED DESCRIPTION

#### Overview

The SGM61030 is a high efficiency step-down switching converter optimized for handheld battery-powered applications. It operates at a quasi-fixed frequency of 2.5MHz and uses adaptive off-time PWM control for the moderate to heavy load range. This allows using a small inductor and small capacitors for compact designs. At light load conditions, SGM61030A operates in power-save mode to reduce the switching frequency and losses for longer battery life. The power-save mode quiescent current is 42µA (TYP) while the shutdown current is only 0.05µA (TYP). For the SGM61030B, it operates in continuous current mode from no load to heavy load.

#### **Power-Save Mode**

At light load conditions, the SGM61030A shifts to the power-save mode and operates with pulse-skip mode to reduce the switching frequency and minimize the losses. It also shuts down most of the internal circuits in

power-save mode. In this mode, one or more PWM pulses are sent to charge the output capacitor and then the switches are kept off. The output capacitor voltage gradually drops due to small load current and when it falls below the nominal voltage threshold, the PWM pulses resume. If the load is still low, the output will go slightly higher than normal again and the switches will be turned off. In power-save mode, the output voltage is slightly higher than nominal output voltage. This effect can be mitigated by a larger output capacitor.

#### **Low Dropout Operation (100% Duty Cycle)**

When the input voltage reduces, the on-time increases. When the input voltage is lower than the regulation output voltage, the output voltage drops, and the SGM61030 goes into 100% duty cycle mode. The high-side switch is always turned on, and the output voltage is determined by the load current times the RDSON composed by the high-side switch and inductor.

# **DETAILED DESCRIPTION (continued)**

#### **Soft-Start and Pre-biased Output**

An 800µs internal soft-start circuit is included to prevent input inrush current and voltage drops during startup. This circuit slowly ramps up the error amplifier reference voltage (VREF = 0.6V) after exiting the shutdown state or under-voltage lockout (UVLO). Slow increase of the output voltage prevents the excessive inrush current for charging the output capacitors and creates a smooth output voltage rise. The other advantage of a soft-start is avoiding supply voltage drops especially on the high internal impedance sources such as the primary cells and rechargeable batteries.

The SGM61030 is also capable of starting with a pre-biased output capacitor when it is powering up or enabled. When the device is turning on, a bias on the output may exist due to the other sources connected to the load(s) such as multi-voltage ICs or simply because of residual charges on the output capacitors. For example, when a device with light load is disabled and re-enabled, the output may not drop during the off period and the device must restart under pre-biased output condition. Without the pre-biased capability, the device may not be able to start up properly. The output ramp is automatically initiated with the bias voltage and ramps up to the nominal output value.

# **Current Limit and Hiccup Mode Short-Circuit Protection**

Limiting the switch current protects the switch itself and also prevents over-current in the source and the inductor. If the high-side (HS) switch current exceeds the  $I_{LIM}$  threshold, HS switch is turned off and the low-side (LS) switch will be turned on to reduce the inductor current and limit the peak.

If 2ms consecutive repetition of this event occurs, the controller will stop switching and turns the output discharge circuit on. Then a new startup will be automatically initiated (hiccup) after 3ms (TYP). The hiccup repeats until the overload or short-circuit fault is cleared.

#### **Under-Voltage Lockout (UVLO)**

Operating with insufficient supply voltage can cause device malfunction or failure. The UVLO protection shuts down the device if the input voltage is below the  $V_{\text{UVLO}}$  threshold. The UVLO comparator has a 200mV hysteresis band.

#### Thermal Shutdown

Thermal protection is included to protect the die against overheating damage. If the junction temperature exceeds  $T_{JSD}$  threshold, the switching stops and the device shuts down. Automatic recovery with a soft-start will begin when the junction temperature drops below the 135°C falling threshold.

#### **Device Enable and Disable**

When the input voltage is valid, pulling the EN input to logic high will enable the device and pulling it low will shut it down. In the shutdown mode, the switches and all control circuits are turned off to reduce the device current to  $0.05\mu A$  (TYP). A  $550k\Omega$  pull-down resistor is internally placed between EN and GND when the device is disabled.

During shutdown, an internal  $42\Omega$  resistor connects SW and GND and softly discharges the output capacitors. This discharge function is also activated when the shutdown is caused by a thermal shutdown, UVLO, or short-circuit protection.

#### **Power Good Output (PG)**

PG is an open-drain output with 1mA sinking capability. This pin should be pulled up with an external resistor to a logic high rail no more than 5.5V unless it is not used. The PG signal is in high-impedance state when the output voltage is in regulation range. PG remains low until  $V_{\text{OUT}}$  exceeds 95% of its nominal (set) value and goes low if  $V_{\text{OUT}}$  drops below 90% of its nominal value. Table 1 shows how the PG state is changed in different conditions.  $V_{\text{PG}}$  is the threshold of the PG hysteretic comparator. It has a 5% hysteresis band and goes high when  $V_{\text{FB}}$  rises above 95% of the  $V_{\text{RFF}}$ .

The PG output is useful for power supply sequencing as well. Usually, the multiple power rails of a system need to be powered in a specific sequence for proper startup. The PG output of the leading power supply is connected to the EN input of the subsequent power supply to implement such sequencing.

**Table 1. PG Output State in Different Conditions**

| Reason               | Condition(s)                   | PG State |              |  |

|----------------------|--------------------------------|----------|--------------|--|

| Reason               | Condition(s)                   | High Z   | Low          |  |

| Output Voltage       | $EN = High, V_{FB} \ge V_{PG}$ | √        |              |  |

| Output voltage       | $EN = High, V_{FB} \le V_{PG}$ |          | <b>V</b>     |  |

| Shutdown by EN       | EN = Low                       |          | $\checkmark$ |  |

| Thermal Shutdown     | $T_J > T_{JSD}$                |          | $\checkmark$ |  |

| UVLO                 | $0.5V < V_{IN} < V_{UVLO}$     |          | <b>V</b>     |  |

| Power Supply Removal | V <sub>IN</sub> ≤ 0.5V         | <b>V</b> |              |  |

#### APPLICATION INFORMATION

In this section, power supply design with the SGM61030 synchronous step-down converter and selection of the external component will be explained based on the typical application that is applicable for various input and output voltage combinations. The SGM61030 does not need any external compensation or feed-forward capacitor.

Figure 3. SGM61030 Circuit for 1.8V Output

#### **Design Requirements**

Table 2 summarizes the requirements for this example as shown in Figure 3. The selected components are given in Table 3.

**Table 2. Design Parameters for the Application Example**

| Design Parameter      | Example Value |

|-----------------------|---------------|

| Input Voltage         | 2.5V to 5.5V  |

| Output Voltage        | 1.8V          |

| Output Current        | ≤ 3A          |

| Output Ripple Voltage | < 30mV        |

Table 3. Selected Components for the Design Example

| Ref              | Description                                                                                                                                                                                | Manufacturer |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| C <sub>IN</sub>  | 10µF, 10V, X7R, 0805, Ceramic<br>P/N: GRM21BR71A106ME51L                                                                                                                                   | Murata       |

| C <sub>OUT</sub> | 22µF, 6.3V, X5R, 0805, Ceramic<br>P/N: GRM21BR60J226ME39L                                                                                                                                  | Murata       |

| L                | $0.47\mu H$ Shielded, DCR <sub>MAX</sub> = $8.4m\Omega$ , $I_{SAT(30\%)}$ = $6.6A$ , $I_{RMS(40^{\circ}C)}$ = $11.2A$ , SRF = $89MHz$ , $4mm \times 4mm \times 1.5mm$ , P/N: XFL4015-471ME | Coilcraft    |

| R <sub>1</sub>   | Value Depends on $V_{OUT}$ , $200k\Omega$ , 1%, $0603$                                                                                                                                     | Standard     |

| R <sub>2</sub>   | 100kΩ, 1%, 0603, 1/16W Chip Resistor                                                                                                                                                       | Standard     |

| R <sub>3</sub>   | 1MΩ, 1%, 0603, 1/16W Chip Resistor                                                                                                                                                         | Standard     |

#### **Output Voltage Setting**

Use Equation 1 to select the  $R_1/R_2$  resistor divider to set the  $V_{OUT}.$  Select the  $R_2$  value less than  $180k\Omega$  to compromise noise sensitivity and light load losses.

$$V_{OUT} = V_{FB} \times \left(1 + \frac{R_1}{R_2}\right) = 0.6V \times \left(1 + \frac{R_1}{R_2}\right)$$

(1)

#### Input Capacitor Selection (C<sub>IN</sub>)

High frequency decoupling input capacitors with low ESR are needed to circulate and absorb the high frequency switching currents of the converter. Place this capacitor right beside the VIN and GND pins. A 10µF ceramic capacitor with X5R or better dielectric and 0805 or smaller size is sufficient in most cases. A larger value can be selected to reduce the input current ripple.

#### **Output Filter Design**

Table 4 can be used to select the proper LC filter components for most design requirements. The inductor initial tolerance can be as high as -30% to +20% of the nominal value and proper current derating is usually required. Bias voltage may cause significant capacitance drops in the ceramic capacitors. The effective deviation of a ceramic capacitor can be as high as -50% to +20% of the nominal value.

$L = 0.47\mu H$  and  $C_{OUT} = 22\mu F$  are the recommended values for the typical application.

**Table 4. Proper Output Capacitor and Inductor Combinations**

| Nominal L | Nominal C <sub>ουτ</sub> (μF) |              |    |     |          |  |  |

|-----------|-------------------------------|--------------|----|-----|----------|--|--|

| (µH)      | 10                            | 22           | 47 | 100 | 150      |  |  |

| 0.47      |                               | √            | √  | √   | √        |  |  |

| 1         | $\checkmark$                  | $\checkmark$ | √  | √   | <b>√</b> |  |  |

| 2.2       |                               |              |    |     |          |  |  |

#### Inductor Selection (L)

The important factors for inductor selection are inductance (L), saturation current ( $I_{SAT}$ ), RMS rating ( $I_{RMS}$ ), DC resistance (DCR) and dimensions. Use Equation 2 to find the inductor peak current ( $I_{L_MAX}$ ) and peak-to-peak ripple current ( $\Delta I_L$ ) in static conditions:

$$\begin{split} I_{L\_MAX} &= I_{O\_MAX} + \frac{\Delta I_L}{2} \\ \Delta I_L &= V_{OUT} \times \frac{1 - D}{L \times f_{e_{WM}}} \end{split} \tag{2}$$

$I_{O\_MAX}$  is the maximum load current, D =  $V_{OUT}/V_{IN}$  represents duty cycle and  $f_{SW}$  is the switching frequency.

Choose the saturation current at least 20% to 30% higher than  $I_{L\_MAX}$ . Larger inductance values reduce the ripple current but lead to sluggish transient response. Some recommended inductors are listed in Table 5.

### **APPLICATION INFORMATION (continued)**

Table 5. Some Suitable Inductors for SGM61030

| L<br>(µH) | I <sub>SAT</sub> (A) | Dimensions<br>L × W × H (mm³) | DCR (TYP)<br>(mΩ) | Part Number              |

|-----------|----------------------|-------------------------------|-------------------|--------------------------|

| 0.47      | 6.6                  | 4 × 4 × 1.5                   | 7.6               | Coilcraft<br>XFL4015-471 |

| 0.47      | 4.7                  | 3.2 × 2.5 × 1.2               | 21                | Toko<br>DFE322512-R47N   |

| 1         | 5.1                  | 4 × 4 × 2                     | 10.8              | Coilcraft<br>XFL4020-102 |

#### **Output Capacitor Selection (COUT)**

This device is capable to operate with low ESR ceramic capacitors to get low voltage ripple and fast response. A  $22\mu F$  capacitor with X7R or X5R dielectric type is recommended. If an output capacitor larger than  $150\mu F$  is used, appropriate startup current reduction should be considered to avoid current limiting or false triggering of the short-circuit protection during startup.

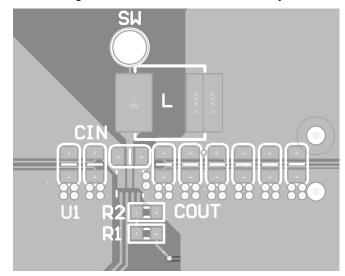

#### **Layout Guidelines**

A good printed-circuit-board (PCB) layout is a critical element of any high performance design. Follow the guidelines below for designing a good layout for the SGM61030.

- Place the input capacitor close to the device with the shortest possible connection traces.

- Share the same GND return point for the input and output capacitors and locate it as close as possible to the device GND pin to minimize the AC current loops.

Place the inductor close to the switching node and connect it with a short trace to minimize the parasitic capacitances coupled to the SW node.

- Keep the signal traces like the FB sense line away from SW or other noisy sources.

- Use GND planes in mid-layers for shielding and minimizing the ground potential drifts.

Refer to Figure 4 for a recommended PCB layout.

Figure 4. SGM61030 Recommended PCB Layout

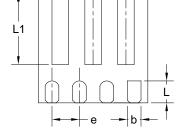

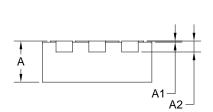

# PACKAGE OUTLINE DIMENSIONS TDFN-2×2-7L

b1-

**TOP VIEW**

SIDE VIEW

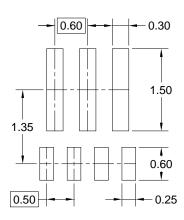

RECOMMENDED LAND PATTERN (Unit: mm)

| Symbol | Dimensions In Millimeters |           |       |  |  |  |

|--------|---------------------------|-----------|-------|--|--|--|

| Symbol | MIN                       | MOD       | MAX   |  |  |  |

| Α      | 0.700                     | 0.750     | 0.800 |  |  |  |

| A1     | 0.000                     | -         | 0.050 |  |  |  |

| A2     |                           | 0.200 REF |       |  |  |  |

| b      | 0.200                     | 0.250     | 0.300 |  |  |  |

| b1     | 0.250                     | 0.300     | 0.350 |  |  |  |

| D      | 1.900                     | 2.000     | 2.100 |  |  |  |

| E      | 1.900                     | 2.000     | 2.100 |  |  |  |

| е      |                           | 0.500 BSC |       |  |  |  |

| e1     | 0.600 BSC                 |           |       |  |  |  |

| L      | 0.300                     | 0.400     | 0.500 |  |  |  |

| L1     | 1.200                     | 1.300     | 1.400 |  |  |  |

NOTE: This drawing is subject to change without notice.

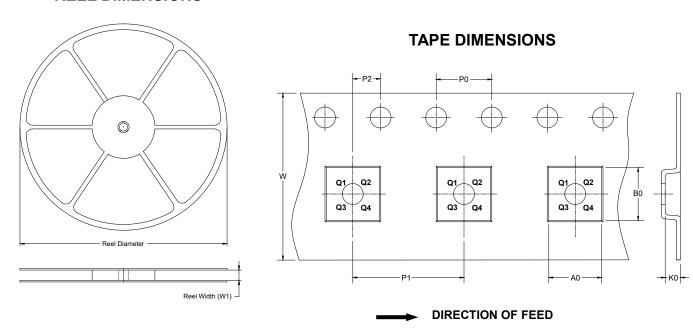

# TAPE AND REEL INFORMATION

#### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| TDFN-2×2-7L  | 7"               | 9.5                      | 2.30       | 2.30       | 1.00       | 4.0        | 4.0        | 2.0        | 8.0       | Q1               |

#### **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

#### **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type   | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |

|-------------|----------------|---------------|----------------|--------------|

| 7" (Option) | 368            | 227           | 224            | 8            |

| 7"          | 442            | 410           | 224            | 18           |