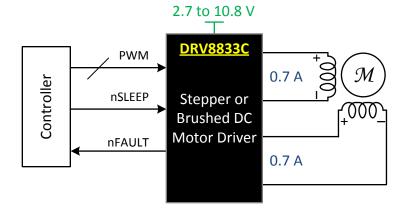

## DRV8833C Dual H-Bridge Motor Driver

## 1 Features

- Dual H-Bridge Motor Driver With Current Control

- 1 or 2 DC Motors or 1 Stepper Motor

- Low On-Resistance: HS + LS = 1735 mΩ (Typical, 25°C)

- Output Current Capability (at V<sub>M</sub> = 5 V, 25°C)

- PWP (HTSSOP) Package

- 0.7-A RMS, 1-A Peak per H-Bridge

- 1.4-A RMS in Parallel Mode

- RTE (QFN) Package

- 0.6-A RMS, 1-A Peak per H-Bridge

- 1.2-A RMS in Parallel Mode

- Wide Power Supply Voltage Range

- 2.7 to 10.8 V

- Integrated Current Regulation

- Easy Pulse-Width-Modulation (PWM) Interface

- 1.6-µA Low-Current Sleep Mode (at 5 V)

- Small Package and Footprint

- 16 HTSSOP (PowerPAD<sup>™</sup>) 5.00 × 6.40 mm

- 16 QFN (PowerPAD) 3.00 × 3.00 mm

- Protection Features

- V<sub>M</sub> Undervoltage Lockout (UVLO)

- Overcurrent Protection (OCP)

- Thermal Shutdown (TSD)

- Fault Indication Pin (nFAULT)

## 2 Applications

- Point-of-Sale Printers

- Video Security Cameras

- Office Automation Machines

- Gaming Machines

- Robotics

- Battery-Powered Toys

## 3 Description

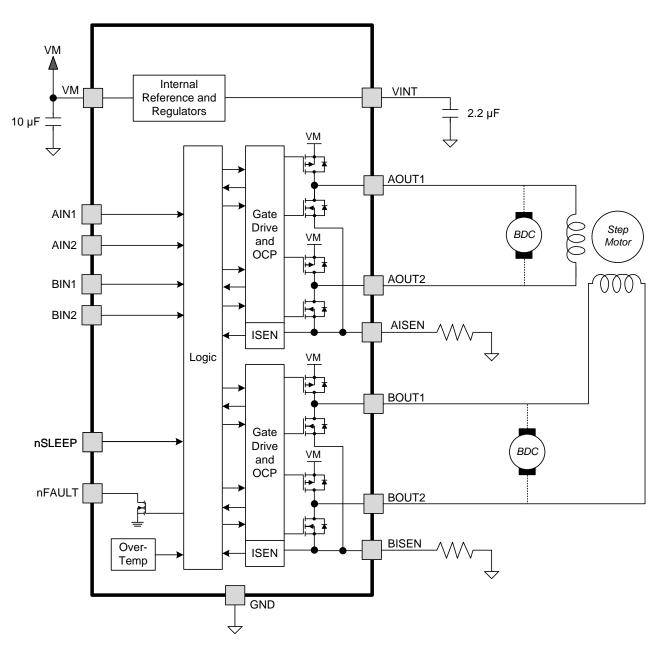

The DRV8833C provides a dual-bridge motor driver solution for toys, printers, and other mechatronic applications.

The device has two H-bridges and can drive two DC brushed motors, a bipolar stepper motor, solenoids, or other inductive loads.

Each H-bridge output consists of a pair of N-channel and P-channel MOSFETs, with circuitry that regulates the winding current. With proper PCB design, each H-bridge of the DRV8833C can drive up to 700-mA RMS (or DC) continuously, at 25°C with a  $V_M$  supply of 5 V. The device can support peak currents of up to 1 A per bridge. Current capability is reduced slightly at lower  $V_M$  voltages.

Internal shutdown functions with a fault output pin are provided for overcurrent protection, short-circuit protection, UVLO, and overtemperature. A low-power sleep mode is also provided.

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE     | BODY SIZE (NOM)   |  |

|-------------|-------------|-------------------|--|

|             | HTSSOP (16) | 5.00 mm × 6.40 mm |  |

| DRV8833C    | QFN (16)    | 3.00 mm × 3.00 mm |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

## **Table of Contents**

| 1 | Feat | tures                            | 1   |

|---|------|----------------------------------|-----|

| 2 | Арр  | lications                        | 1   |

| 3 | Des  | cription                         | 1   |

| 4 | Rev  | ision History                    | 2   |

| 5 | Pin  | Configuration and Functions      | 3   |

| 6 | Spe  | cifications                      | 4   |

|   | 6.1  | Absolute Maximum Ratings         | . 4 |

|   | 6.2  | Handling Ratings                 | . 4 |

|   | 6.3  | Recommended Operating Conditions |     |

|   | 6.4  | Thermal Information              | . 5 |

|   | 6.5  | Electrical Characteristics       | . 5 |

|   | 6.6  | Typical Characteristics          | . 7 |

| 7 | Deta | ailed Description                | 8   |

|   | 7.1  | Overview                         | . 8 |

|   | 7.2  | Functional Block Diagram         | . 8 |

|   |      |                                  |     |

|    | 7.3  | Feature Description                               | . 9 |

|----|------|---------------------------------------------------|-----|

|    | 7.4  | Device Functional Modes                           | 13  |

| 8  | Арр  | lication and Implementation                       | 14  |

|    | 8.1  | Application Information                           | 14  |

|    | 8.2  | Typical Application                               | 14  |

| 9  | Pow  | er Supply Recommendations                         | 17  |

|    | 9.1  | Sizing Bulk Capacitance for Motor Drive Systems . | 17  |

| 10 | Lay  | out                                               | 18  |

|    | 10.1 | Layout Guidelines                                 | 18  |

|    | 10.2 | Layout Example                                    | 18  |

| 11 | Dev  | ice and Documentation Support                     | 19  |

|    | 11.1 | Trademarks                                        | 19  |

|    | 11.2 | Electrostatic Discharge Caution                   | 19  |

|    | 11.3 | Glossary                                          | 19  |

| 12 |      | hanical, Packaging, and Orderable mation          | 19  |

## 4 Revision History

| DATE        | REVISION | NOTES            |

|-------------|----------|------------------|

| August 2014 | *        | Initial release. |

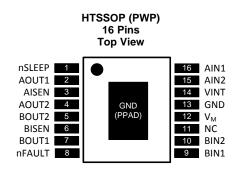

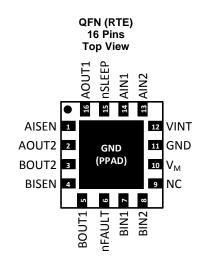

## 5 Pin Configuration and Functions

#### Pin Functions

| PIN            |        | ТҮРЕ | DESCRIPTION |                            |                                                                                                       |  |

|----------------|--------|------|-------------|----------------------------|-------------------------------------------------------------------------------------------------------|--|

| NAME           | PWP    | RTE  | ITPE        |                            | DESCRIPTION                                                                                           |  |

| POWER A        | ND GRO | UND  |             |                            |                                                                                                       |  |

| GND            | 13     | 11   | PWR         | Device ground              | Both the GND pin and device PowerPAD must be connected to ground                                      |  |

| VINT           | 14     | 12   | _           | Internal regulator (3.3 V) | Internal supply voltage; bypass to GND with 2.2-µF, 6.3-V capacitor                                   |  |

| V <sub>M</sub> | 12     | 10   | PWR         | Power supply               | Connect to motor supply voltage; bypass to GND with a 10- $\mu F$ (minimum) capacitor rated for $V_M$ |  |

| CONTROL        | _      |      |             |                            |                                                                                                       |  |

| AIN1           | 16     | 14   |             | Libridge A DVA(Misseut     | Controls the state of AOUTA and AOUTO, internal culldown                                              |  |

| AIN2           | 15     | 13   |             | H-bridge A PWM input       | Controls the state of AOUT1 and AOUT2; internal pulldown                                              |  |

| BIN1           | 9      | 7    |             | Li bridge D DW/M input     | Controle the state of POULT1 and POULT2; internal nulldown                                            |  |

| BIN2           | 10     | 8    |             | H-bridge B PWM input       | tt Controls the state of BOUT1 and BOUT2; internal pulldown                                           |  |

| nSLEEP         | 1      | 15   | I           | Sleep mode input           | Logic high to enable device; logic low to enter low-power sleep mode; internal pulldown               |  |

| STATUS         |        |      |             |                            |                                                                                                       |  |

| nFAULT         | 8      | 6    | OD          | Fault indication pin       | Pulled logic low with fault condition; open-drain output requires an external pullup                  |  |

| OUTPUT         |        |      |             |                            |                                                                                                       |  |

| AISEN          | 3      | 1    | 0           | Bridge A sense             | Sense resistor to GND sets PWM current regulation level (see <i>PWM Motor Drivers</i> )               |  |

| AOUT1          | 2      | 16   | 0           |                            |                                                                                                       |  |

| AOUT2          | 4      | 2    | 0           | Bridge A output            | Positive current is AOUT1 $\rightarrow$ AOUT2                                                         |  |

| BISEN          | 6      | 4    | 0           | Bridge B sense             | Sense resistor to GND sets PWM current regulation level (see <i>PWM</i><br><i>Motor Drivers</i> )     |  |

| BOUT1          | 7      | 5    | 0           | Pridao P. output           |                                                                                                       |  |

| BOUT2          | 5      | 3    | 0           | Bridge B output            | Positive current is BOUT1 $\rightarrow$ BOUT2                                                         |  |

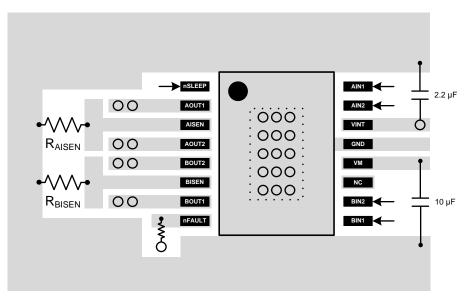

### External Components

| Component                                                  | Pin 1                                                                                       | Pin 2                           | Recommended                                        |  |  |  |

|------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------|----------------------------------------------------|--|--|--|

| C <sub>VM</sub>                                            | $C_{VM}$ $V_M$ GND $10-\mu F^{(1)}$ ceramic capacitor rated for $V_M$                       |                                 |                                                    |  |  |  |

| C <sub>VINT</sub> VINT GND 6.3-V, 2.2-µF ceramic capacitor |                                                                                             | 6.3-V, 2.2-μF ceramic capacitor |                                                    |  |  |  |

| R <sub>nFAULT</sub>                                        | VINT <sup>(2)</sup>                                                                         | nFAULT                          | >1 kΩ                                              |  |  |  |

| R <sub>AISEN</sub>                                         | R <sub>AISEN</sub> AISEN GND Sense resistor, see <i>Typical Application</i> for sizing      |                                 | Sense resistor, see Typical Application for sizing |  |  |  |

| R <sub>BISEN</sub>                                         | RBISEN         BISEN         GND         Sense resistor, see Typical Application for sizing |                                 | Sense resistor, see Typical Application for sizing |  |  |  |

Proper bulk capacitance sizing depends on the motor power. (1)

nFAULT may be pulled up to an external supply rated < 5.5 V. (2)

#### **Specifications** 6

### 6.1 Absolute Maximum Ratings

over operating free-air temperature (unless otherwise noted) (1)

|         |                                                               | MIN    | MAX                  | UNIT |

|---------|---------------------------------------------------------------|--------|----------------------|------|

|         | Power supply (V <sub>M</sub> )                                | -0.3   | 11.8                 | V    |

|         | Internal regulator (VINT)                                     | -0.3   | 3.8                  | V    |

|         | Control pins (AIN1, AIN2, BIN1, BIN2, nSLEEP, nFAULT)         | -0.3   | 7                    | V    |

| Voltage | Continuous phase node pins (AOUT1, AOUT2, BOUT1, BOUT2)       | -0.3   | V <sub>M</sub> + 0.5 | V    |

|         | Pulsed 10 µs phase node pins (AOUT1, AOUT2, BOUT1, BOUT2)     | -1     | V <sub>M</sub> + 1   | V    |

|         | Continuous shunt amplifier input pins (AISEN, BISEN)          | -0.3   | 0.5                  | V    |

|         | Pulsed 10 µs shunt amplifier input pins (AISEN, BISEN)        | -1     | 1                    | V    |

|         | Peak drive current (AOUT1, AOUT2, BOUT1, BOUT2, AISEN, BISEN) | Intern | ally limited         | А    |

| TJ      | Operating junction temperature                                | -40    | 150                  | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 6.2 Handling Ratings

|                    |                |                                                                                          | MIN   | MAX  | UNIT |

|--------------------|----------------|------------------------------------------------------------------------------------------|-------|------|------|

| T <sub>stg</sub>   | Storage temper | ature range                                                                              | -65   | 150  | °C   |

| V                  | Electrostatic  | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>              | -2000 | 2000 | V    |

| V <sub>(ESD)</sub> | discharge      | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins <sup>(2)</sup> | -1000 | 1000 | v    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. (2)

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                           |               | MIN | MAX  | UNIT |

|----------------|-------------------------------------------|---------------|-----|------|------|

| VM             | Power supply voltage range <sup>(1)</sup> |               | 2.7 | 10.8 | V    |

| VI             | Logic level input voltage                 |               | 0   | 5.5  | V    |

|                | Motor RMS current <sup>(2)</sup>          | PWP package   | 0   | 0.7  | А    |

| IRMS           |                                           | RTE package   | 0   | 0.6  | А    |

| $f_{PWM}$      | Applied PWM signal to AIN1, AIN2, E       | 3IN1, or BIN2 | 0   | 200  | kHz  |

| T <sub>A</sub> | Operating ambient temperature             |               | -40 | 85   | °C   |

Note that when  $V_M$  is below 5 V,  $R_{DS(ON)}$  increases and maximum output current is reduced. Power dissipation and thermal limits must be observed. (1)

(2)

## 6.4 Thermal Information

|                       |                                              | DRV8    | 8833C   |      |

|-----------------------|----------------------------------------------|---------|---------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | HTSSOP  | QFN     | UNIT |

|                       |                                              | 16 PINS | 16 PINS |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 40.5    | 44.7    |      |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 32.9    | 48.5    |      |

| $R_{	extsf{	heta}JB}$ | Junction-to-board thermal resistance         | 28.8    | 16.8    | °C/W |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.6     | 0.7     | C/VV |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 11.5    | 16.7    |      |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 4.8     | 4.2     |      |

(1) For more information about traditional and new thermal metrics, see the *IC Package Thermal Metrics* application report, SPRA953.

### 6.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                                | TEST CONDITIONS                                                                                     | MIN | ТҮР  | MAX  | UNIT |

|---------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------|-----|------|------|------|

| POWER S             | SUPPLIES (V <sub>M</sub> , VINT)         |                                                                                                     |     |      |      |      |

| V <sub>M</sub>      | V <sub>M</sub> operating voltage         |                                                                                                     | 2.7 |      | 10.8 | V    |

| I <sub>VM</sub>     | V <sub>M</sub> operating supply current  | $V_{M} = 5 V$ , xINx low, nSLEEP high                                                               |     | 1.7  | 3    | mA   |

| I <sub>VMQ</sub>    | V <sub>M</sub> sleep mode supply current | $V_{M} = 5 V$ , nSLEEP low                                                                          |     | 1.6  | 2.7  | μA   |

| t <sub>SLEEP</sub>  | Sleep time                               | nSLEEP low to sleep mode                                                                            |     | 10   |      | μs   |

| WAKE                | Wake-up time                             | nSLEEP high to output transition                                                                    |     | 155  |      | μs   |

| t <sub>ON</sub>     | Turn-on time                             | $V_M > V_{UVLO}$ to output transition                                                               |     | 25   |      | μs   |

| VINT                | Internal regulator voltage               | V <sub>M</sub> = 5 V                                                                                | 3   | 3.3  | 3.6  | V    |

| CONTRO              | L INPUTS (AIN1, AIN2, BIN1, BIN2, I      | SLEEP)                                                                                              |     |      |      |      |

|                     | land la cie la constructo                | xINx                                                                                                | 0   |      | 0.7  |      |

| V <sub>IL</sub>     | Input logic low voltage                  | nSLEEP                                                                                              | 0   |      | 0.5  | V    |

|                     | have at the set of the sector of the sec | xINx                                                                                                | 2   |      | 5.5  | N/   |

| V <sub>IH</sub>     | Input logic high voltage                 | nSLEEP                                                                                              | 2.5 |      | 5.5  | V    |

| V <sub>HYS</sub>    | Input logic hysteresis                   |                                                                                                     | 350 | 400  | 650  | mV   |

| IL                  | Input logic low current                  | V <sub>IN</sub> = 0 V                                                                               | -1  |      | 1    | μA   |

| н                   | Input logic high current                 | V <sub>IN</sub> = 5 V                                                                               |     |      | 50   | μA   |

| 2                   | <b>5</b> 84 4 4 4                        | xINx                                                                                                | 100 | 150  | 250  |      |

| R <sub>PD</sub>     | Pulldown resistance                      | nSLEEP                                                                                              | 380 | 500  | 750  | kΩ   |

| DEG                 | Input deglitch time                      |                                                                                                     |     | 575  |      | ns   |

| PROP                | Propagation delay INx to OUTx            | V <sub>M</sub> = 5 V                                                                                |     | 1.2  |      | μs   |

|                     | L OUTPUTS (nFAULT)                       |                                                                                                     | ų.  |      | 1    |      |

| V <sub>OL</sub>     | Output logic low voltage                 | I <sub>O</sub> = 5 mA                                                                               |     |      | 0.5  | V    |

| ОН                  | Output logic high leakage                | $R_{PULLUP} = 1 \ k\Omega \ to \ 5 \ V$                                                             | -1  |      | 1    | μA   |

|                     | DRIVER OUTPUTS (AOUT1, AOUT2,            | BOUT1, BOUT2)                                                                                       |     |      |      |      |

|                     |                                          | V <sub>M</sub> = 5 V, I = 0.2 A, T <sub>A</sub> = 25°C                                              |     | 1180 |      |      |

| -                   |                                          | $V_{M} = 5 V, I = 0.2 A, T_{A} = 85^{\circ}C^{(1)}$                                                 |     | 1400 | 1475 |      |

| R <sub>DS(ON)</sub> | High-side FET on-resistance              | V <sub>M</sub> = 2.7 V, I = 0.2 A, T <sub>A</sub> = 25°C                                            |     | 1550 |      | mΩ   |

|                     |                                          | $V_{M} = 2.7 V, I = 0.2 A, T_{A} = 85^{\circ}C^{(1)}$                                               |     | 1875 | 1975 |      |

|                     |                                          | V <sub>M</sub> = 5 V, I = 0.2 A, T <sub>A</sub> = 25°C                                              |     | 555  |      |      |

|                     |                                          | $V_{\rm M} = 5 \text{ V}, \text{ I} = 0.2 \text{ A}, \text{ T}_{\rm A} = 85^{\circ} \text{C}^{(1)}$ |     | 675  | 705  |      |

| R <sub>DS(ON)</sub> | Low-side FET on-resistance               | V <sub>M</sub> = 2.7 V, I = 0.2 A, T <sub>A</sub> = 25°C                                            |     | 635  |      | mΩ   |

|                     |                                          | $V_{M} = 2.7 V, I = 0.2 A, T_{A} = 85^{\circ}C^{(1)}$                                               |     | 775  | 815  |      |

## **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

|                                 | PARAMETER                              | TEST CONDITIONS                                              | MIN | TYP | MAX | UNIT |

|---------------------------------|----------------------------------------|--------------------------------------------------------------|-----|-----|-----|------|

| I <sub>OFF</sub>                | Off-state leakage current              | V <sub>M</sub> = 5 V                                         | -1  |     | 1   | μA   |

| t <sub>RISE</sub>               | Output rise time                       | $V_{\rm M}$ = 5 V; $R_{\rm L}$ = 16 $\Omega$ to GND          |     | 70  |     | ns   |

| t <sub>FALL</sub>               | Output fall time                       | $V_M = 5 \text{ V}; \text{ R}_L = 16 \Omega \text{ to } V_M$ |     | 80  |     | ns   |

| t <sub>DEAD</sub>               | Output dead time                       | Internal dead time                                           |     | 450 |     | ns   |

| PWM CUR                         | RENT CONTROL (AISEN, BISEN)            |                                                              |     |     |     |      |

| V <sub>TRIP</sub>               | xISEN trip voltage                     |                                                              | 160 | 200 | 240 | mV   |

| t <sub>OFF</sub>                | Current control constant off time      | Internal PWM constant off time                               |     | 20  |     | μs   |

| PROTECTI                        | ON CIRCUITS                            |                                                              |     |     | ÷   |      |

|                                 |                                        | V <sub>M</sub> falling; UVLO report                          |     |     | 2.6 |      |

| V <sub>UVLO</sub>               | V <sub>M</sub> undervoltage lockout    | V <sub>M</sub> rising; UVLO recovery                         |     |     | 2.7 | V    |

| V <sub>UVLO,HYS</sub>           | V <sub>M</sub> undervoltage hysteresis | Rising to falling threshold                                  |     | 90  |     | mV   |

| I <sub>OCP</sub>                | Overcurrent protection trip level      |                                                              | 1   |     |     | А    |

| t <sub>DEG</sub>                | Overcurrent deglitch time              |                                                              |     | 2.3 |     | μs   |

| t <sub>OCP</sub>                | Overcurrent protection period          |                                                              |     | 1.4 |     | ms   |

| T <sub>TSD</sub> <sup>(2)</sup> | Thermal shutdown temperature           | Die temperature, T <sub>J</sub>                              | 150 |     |     | °C   |

| T <sub>HYS</sub>                | Thermal shutdown hysteresis            | Die temperature, T <sub>J</sub>                              |     | 20  |     | °C   |

(2) Not tested in production; based on design and characterization data

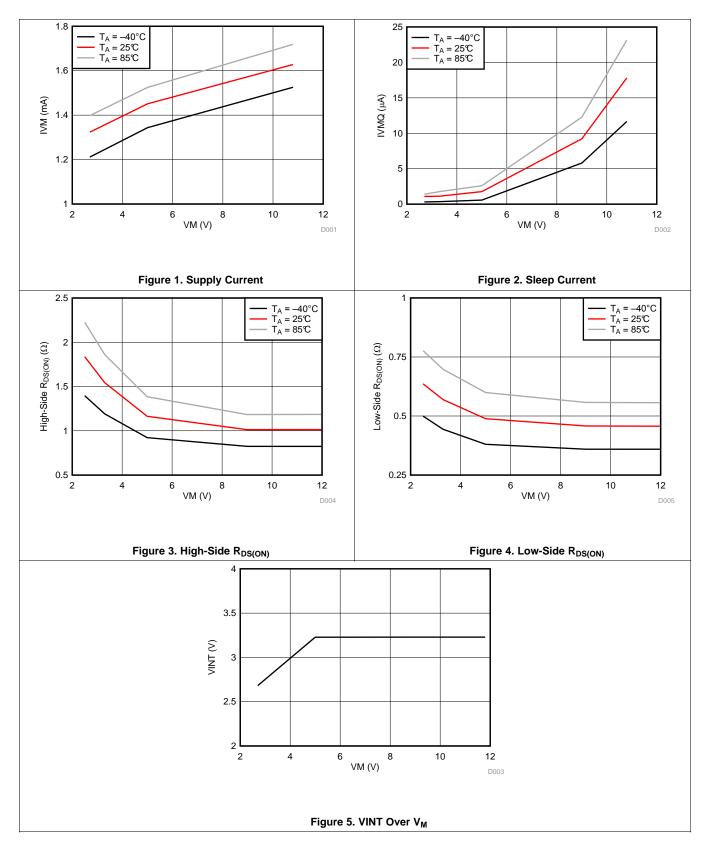

## 6.6 Typical Characteristics

## 7 Detailed Description

## 7.1 Overview

The DRV8833C device is an integrated motor driver solution for brushed DC or bipolar stepper motors. The device integrates two PMOS + NMOS H-bridges and current regulation circuitry. The DRV8833C can be powered with a supply voltage from 2.7 to 10.8 V and can provide an output current up to 700 mA RMS.

A simple PWM interface allows easy interfacing to the controller circuit.

The current regulation is a 20-µs fixed off-time slow decay.

The device includes a low-power sleep mode, which lets the system save power when not driving the motor.

## 7.2 Functional Block Diagram

## 7.3 Feature Description

## 7.3.1 PWM Motor Drivers

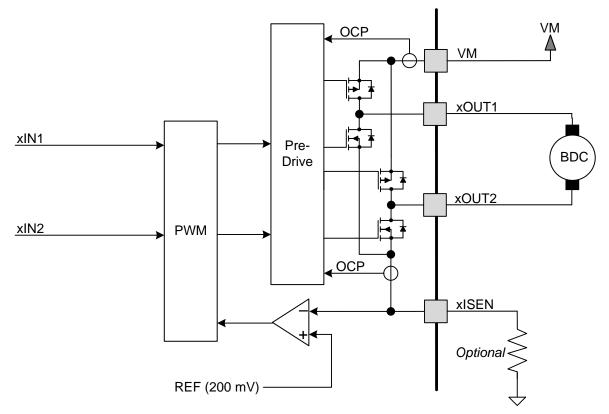

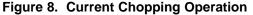

The DRV8833C contains drivers for two full H-bridges. Figure 6 shows a block diagram of the circuitry.

Figure 6. H-Bridge and Current-Chopping Circuitry

## 7.3.2 Bridge Control and Decay Modes

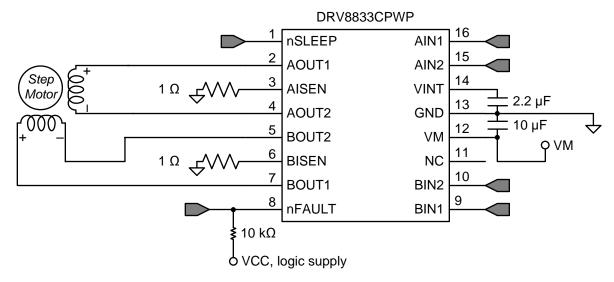

The AIN1 and AIN2 input pins control the state of the AOUT1 and AOUT2 outputs; similarly, the BIN1 and BIN2 input pins control the state of the BOUT1 and BOUT2 outputs (see Table 1).

|      | <u> </u> |       |       |                    |  |  |  |  |  |  |

|------|----------|-------|-------|--------------------|--|--|--|--|--|--|

| xIN1 | xIN2     | xOUT1 | xOUT2 | FUNCTION           |  |  |  |  |  |  |

| 0    | 0        | Z     | Z     | Coast / fast decay |  |  |  |  |  |  |

| 0    | 1        | L     | Н     | Reverse            |  |  |  |  |  |  |

| 1    | 0        | Н     | L     | Forward            |  |  |  |  |  |  |

| 1    | 1        | L     | L     | Brake / slow decay |  |  |  |  |  |  |

| 1    | 1        | L     | L     | Brake / slow decay |  |  |  |  |  |  |

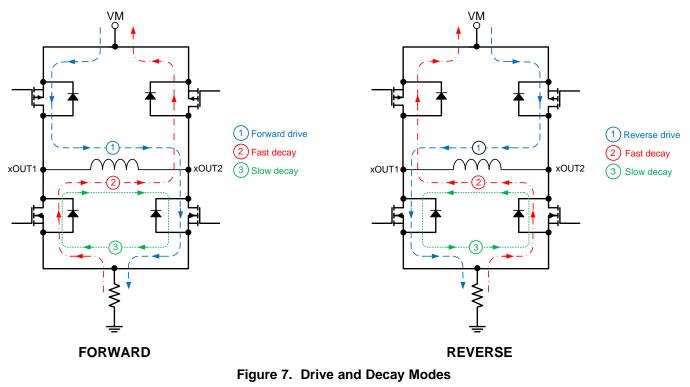

### Table 1. H-Bridge Logic

The inputs can also be used for PWM control of the motor speed. When controlling a winding with PWM and the drive current is interrupted, the inductive nature of the motor requires that the current must continue to flow (called recirculation current). To handle this recirculation current, the H-bridge can operate in two different states, fast decay or slow decay. In fast-decay mode, the H-bridge is disabled and recirculation current flows through the body diodes. In slow-decay mode, the motor winding is shorted by enabling both low-side FETs.

To externally pulse-width modulate the bridge in fast-decay mode, the PWM signal is applied to one xIN pin while the other is held low; to use slow-decay mode, one xIN pin is held high. See Table 2 for more information.

| xIN1 | xIN2 | FUNCTION                |

|------|------|-------------------------|

| PWM  | 0    | Forward PWM, fast decay |

| 1    | PWM  | Forward PWM, slow decay |

| 0    | PWM  | Reverse PWM, fast decay |

| PWM  | 1    | Reverse PWM, slow decay |

| Table 2. PWM Control of Motor S | peed |

|---------------------------------|------|

|---------------------------------|------|

The internal current control is still enabled when applying external PWM to xIN. To disable the current control when applying external PWM, the xISEN pins should be connected directly to ground. Figure 7 show the current paths in different drive and decay modes.

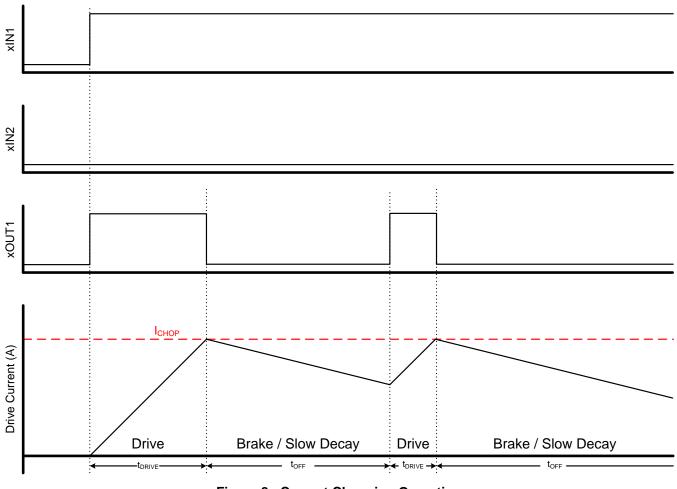

### 7.3.3 Current Control

The current through the motor windings may be limited, or controlled, by a 20-µs constant off-time PWM current regulation, or current chopping. For DC motors, current control is used to limit the start-up and stall current of the motor. For stepper motors, current control is often used at all times.

When an H-bridge is enabled, current rises through the winding at a rate dependent on the DC voltage and inductance of the winding. If the current reaches the current chopping threshold, the bridge disables the current until the beginning of the next PWM cycle. Note that immediately after the output is enabled, the voltage on the xISEN pin is ignored for a fixed period of time before enabling the current sense circuitry. This blanking time is fixed at 3.75  $\mu$ s.

The PWM chopping current is set by a comparator that compares the voltage across a current sense resistor connected to the xISEN pins with a reference voltage. The reference voltage,  $V_{TRIP}$ , is is fixed at 200 mV nominally.

The chopping current is calculated as in Equation 1.

$$I_{CHOP} = \frac{200 \text{ mV}}{R_{XISEN}}$$

Example: If a 1- $\Omega$  sense resistor is used, the chopping current will be 200 mV / 1  $\Omega$  = 200 mA.

(1)

#### NOTE

If current control is not needed, the xISEN pins should be connected directly to ground.

#### 7.3.4 Decay Mode

After the chopping current threshold is reached, the H-bridge switches to slow-decay mode. This state is held for  $t_{off}$  (20 µs) until the next cycle to turn on the high-side MOSFETs.

#### 7.3.5 Slow Decay

In slow-decay mode, the high-side MOSFETs are turned off and both of the low-side MOSFETs are turned on. The motor current decreases while flowing in the two low-side MOSFETs until reaching its fixed off time (typically 20 µs). After that, the high-side MOSFETs are enabled to increase the winding current again.

#### 7.3.6 Sleep Mode

Driving nSLEEP low puts the device into a low-power sleep state. In this state, the H-bridges are disabled, all internal logic is reset, and all internal clocks are stopped. All inputs are ignored until nSLEEP returns inactive high. When returning from sleep mode, some time,  $t_{WAKE}$ , needs to pass before the motor driver becomes fully operational. To make the board design simple, the nSLEEP can be pulled up to the supply (V<sub>M</sub>). TI recommends to use a pullup resistor when this is done. This resistor limits the current to the input in case V<sub>M</sub> is higher than 6.5 V. Internally, the nSLEEP pin has a 500-k $\Omega$  resistor to GND. It also has a clamping Zener diode that clamps the voltage at the pin at 6.5 V. Currents greater than 250  $\mu$ A can cause damage to the input structure. Therefore, TI recommends a pullup resistor between 20 to 75 k $\Omega$ .

#### 7.3.7 Parallel Mode

The two H-bridges in the DRV8833C can be connected in parallel for double the current of a single H-bridge. The internal dead time in the DRV8833C prevents any risk of cross-conduction (shoot-through) between the two bridges due to timing differences between the two bridges. Figure 9 shows the connections.

Figure 9. Parallel Mode Schematic

#### 7.3.8 Protection Circuits

The DRV8833C is fully protected against overcurrent, overtemperature, and undervoltage events.

#### 7.3.8.1 Overcurrent Protection (OCP)

An analog current limit ( $I_{OCP}$ ) circuit on each FET limits the current through the FET by limiting the gate drive. If this analog current limit persists for longer than the OCP deglitch time ( $t_{DEG}$ ), all FETs in the H-bridge are disabled and the nFAULT pin is driven low. The driver is re-enabled after the OCP retry period ( $t_{OCP}$ ) has passed. nFAULT becomes high again after the retry time. If the fault condition is still present, the cycle repeats. If the fault is no longer present, normal operation resumes and nFAULT remains deasserted. Note that only the H-bridge in which the OCP is detected will be disabled while the other bridge functions normally.

Overcurrent conditions are detected independently on both high-side and low-side devices; a short to ground, supply, or across the motor winding all result in an overcurrent shutdown. Note that overcurrent protection does not use the current sense circuitry used for PWM current control, so it functions even without presence of the xISEN resistors.

#### 7.3.8.2 Thermal Shutdown (TSD)

If the die temperature exceeds safe limits, all FETs in the H-bridge are disabled and the nFAULT pin is driven low. After the die temperature has fallen below the specified hysteresis ( $T_{HYS}$ ), operation automatically resumes. The nFAULT pin is released after operation has resumed.

### 7.3.8.3 UVLO

If at any time the voltage on the  $V_M$  pin falls below the UVLO threshold voltage,  $V_{UVLO}$ , all circuitry in the device is disabled, and all internal logic is reset. Operation resumes when  $V_M$  rises above the UVLO threshold. The nFAULT pin is not driven low during an undervoltage condition.

| Fault                              | Condition              | Error Report | H-Bridge | Internal Circuits | Recovery                  |  |  |  |  |  |

|------------------------------------|------------------------|--------------|----------|-------------------|---------------------------|--|--|--|--|--|

| V <sub>M</sub> undervoltage (UVLO) | V <sub>M</sub> < 2.6 V | None         | Disabled | Disabled          | $V_{M} > 2.7 V$           |  |  |  |  |  |

| Overcurrent (OCP)                  | $I_{OUT} > I_{OCP}$    | FAULTn       | Disabled | Operating         | OCP                       |  |  |  |  |  |

| Thermal Shutdown (TSD)             | $T_J > T_{TSD}$        | FAULTn       | Disabled | Operating         | $T_J < T_{TSD} - T_{HYS}$ |  |  |  |  |  |

## Table 3. Device Protection

## 7.4 Device Functional Modes

The DRV8833C is active unless the nSLEEP pin is brought logic low. In sleep mode, the H-bridge FETs are disabled (Hi-Z). Note that  $t_{SLEEP}$  must elapse after a falling edge on the nSLEEP pin before the device is in sleep mode. The DRV8833C is brought out of sleep mode automatically if nSLEEP is brought logic high. Note that  $t_{WAKE}$  must elapse before the outputs change state after wake-up.

#### Table 4. Modes of Operation

| Fault             | Condition               | H-Bridge  | Internal Circuits |

|-------------------|-------------------------|-----------|-------------------|

| Operating         | nSLEEP pin high         | Operating | Operating         |

| Sleep mode        | nSLEEP pin low          | Disabled  | Disabled          |

| Fault encountered | Any fault condition met | Disabled  | See Table 3       |

## 8 Application and Implementation

## 8.1 Application Information

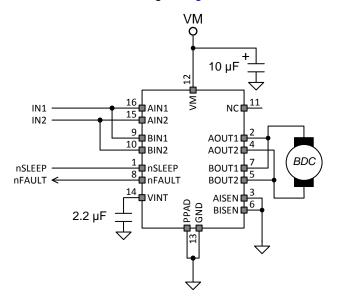

The DRV8833C is used in stepper or brushed DC motor control. The following design procedure can be used to configure the DRV8833C in a bipolar stepper motor application.

## 8.2 Typical Application

#### 8.2.1 Design Requirements

Table 5 gives design input parameters for system design.

| -                        |                   |                   |  |  |  |  |  |  |  |

|--------------------------|-------------------|-------------------|--|--|--|--|--|--|--|

| Design Parameter         | Reference         | Example Value     |  |  |  |  |  |  |  |

| Supply voltage           | V <sub>M</sub>    | 9 V               |  |  |  |  |  |  |  |

| Motor winding resistance | RL                | 12 Ω/phase        |  |  |  |  |  |  |  |

| Motor winding inductance | L                 | 10 mH/phase       |  |  |  |  |  |  |  |

| Motor full step angle    | θ <sub>step</sub> | 1.8 °/step        |  |  |  |  |  |  |  |

| Target stepping level    | n <sub>m</sub>    | 2 (half-stepping) |  |  |  |  |  |  |  |

| Target motor speed       | v                 | 120 rpm           |  |  |  |  |  |  |  |

| Target chopping current  | I <sub>CHOP</sub> | 200 mA            |  |  |  |  |  |  |  |

| Sense resistor           | R <sub>ISEN</sub> | 1 Ω               |  |  |  |  |  |  |  |

Table 5. Design Parameters

#### 8.2.2 Detailed Design Procedure

#### 8.2.2.1 Stepper Motor Speed

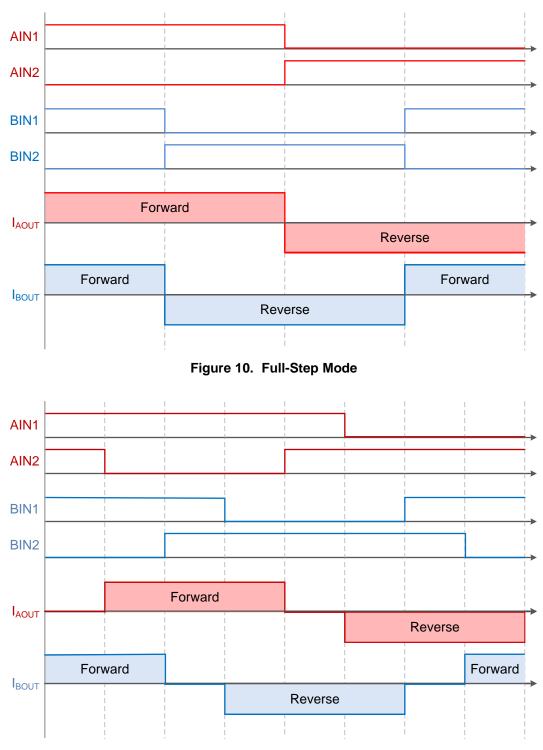

The first step in configuring the DRV8833C requires the desired motor speed and stepping level. The DRV8833C can support full- and half-stepping modes using the PWM interface.

If the target motor speed is too high, the motor does not spin. Ensure that the motor can support the target speed.

For a desired motor speed (v), microstepping level ( $n_m$ ), and motor full step angle ( $\theta_{step}$ ),

$$f_{\text{step}} (\text{steps / s}) = \frac{v(\text{rpm}) \times n_{\text{m}} (\text{steps}) \times 360^{\circ} / \text{rot}}{\theta_{\text{step}} (^{\circ} / \text{step}) \times 60 \text{ s / min}}$$

(2)

Figure 11. Half-Step Mode

## 8.2.2.2 Current Regulation

The chopping current ( $I_{CHOP}$ ) is the maximum current driven through either winding. This quantity depends on the sense resistor value ( $R_{XISEN}$ ).

$$I_{CHOP} = \frac{200 \text{ mV}}{R_{XISEN}}$$

#### DRV8833C SLVSCP9-AUGUST 2014

$I_{CHOP}$  is set by a comparator which compares the voltage across  $R_{XISEN}$  to a reference voltage. Note that  $I_{CHOP}$  must follow Equation 4 to avoid saturating the motor.

$$I_{FS} (A) < \frac{VM (V)}{R_{L} (\Omega) + R_{DS(ON)} HS (\Omega) + R_{DS(ON)} LS (\Omega)}$$

where

- V<sub>M</sub> is the motor supply voltage.

- $R_L$  is the motor winding resistance.

#### 8.2.3 Application Curve

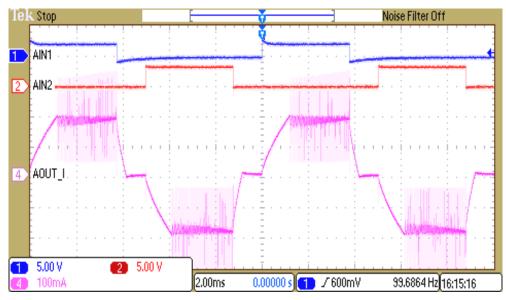

A. Channel 1 is the AIN1 input PWM signal, and channel 2 is the AIN2 input PWM signal. BIN1 and BIN2 follow the same pattern, but are shifted by 90° from AIN1 and AIN2 as shown in Figure 11. Channel 4 is the output current in the direction AOUT1 → AOUT2. In forward and reverse drive, the current rises until it hits the current chopping limit of 200 mA, and is regulated at that level with fixed-off time current chopping.

#### (4)

## 9 Power Supply Recommendations

The DRV8833C is designed to operate from an input voltage supply ( $V_M$ ) range between 2.7 to 10.8 V. A 10- $\mu$ F ceramic capacitor rated for  $V_M$  must be placed as close to the DRV8833C as possible.

## 9.1 Sizing Bulk Capacitance for Motor Drive Systems

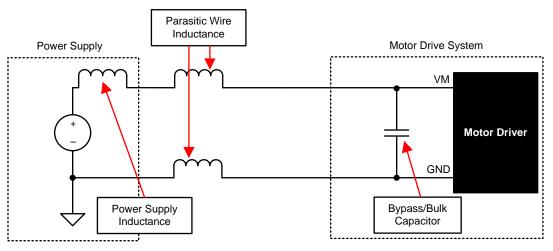

Bulk capacitance sizing is an important factor in motor drive system design. It depends on a variety of factors including:

- Type of power supply

- Acceptable supply voltage ripple

- · Parasitic inductance in the power supply wiring

- Type of motor (brushed DC, brushless DC, stepper)

- Motor startup current

- Motor braking method

The inductance between the power supply and motor drive system limits the rate current can change from the power supply. If the local bulk capacitance is too small, the system responds to excessive current demands or dumps from the motor with a change in voltage. Size the bulk capacitance to meet acceptable voltage ripple levels.

The data sheet generally provides a recommended value, but system-level testing is required to determine the appropriate-sized bulk capacitor.

Figure 13. Setup of Motor Drive System With External Power Supply

## 10 Layout

### 10.1 Layout Guidelines

Bypass the V<sub>M</sub> terminal to GND using a low-ESR ceramic bypass capacitor with a recommended value of 10  $\mu$ F rated for V<sub>M</sub>. This capacitor should be placed as close to the V<sub>M</sub> pin as possible with a thick trace or ground plane connection to the device GND pin and PowerPAD.

Bypass VINT to ground with a ceramic capacitor rated 6.3 V. Place this bypassing capacitor as close to the pin as possible.

#### **10.2 Layout Example**

## **11** Device and Documentation Support

## 11.1 Trademarks

PowerPAD is a trademark of Texas Instruments.

## **11.2 Electrostatic Discharge Caution**

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## 11.3 Glossary

SLYZ022 — TI Glossary.

This glossary lists and explains terms, acronyms, and definitions.

## 12 Mechanical, Packaging, and Orderable Information

The following pages include mechanical, packaging, and orderable information. This information is the most current data available for the designated devices. This data is subject to change without notice and revision of this document. For browser-based versions of this data sheet, refer to the left-hand navigation.

## PACKAGE OPTION ADDENDUM

19-Nov-2014

## **PACKAGING INFORMATION**

| Orderable Device | Status | Package Type | •       | Pins | Package | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp       | Op Temp (°C) | Device Marking | Samples |

|------------------|--------|--------------|---------|------|---------|----------------------------|------------------|---------------------|--------------|----------------|---------|

|                  | (1)    |              | Drawing |      | Qty     | (2)                        | (6)              | (3)                 |              | (4/5)          |         |

| DRV8833CPWP      | ACTIVE | HTSSOP       | PWP     | 16   | 90      | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR | -40 to 85    | 8833C          | Samples |

| DRV8833CPWPR     | ACTIVE | HTSSOP       | PWP     | 16   | 2000    | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-3-260C-168 HR | -40 to 85    | 8833C          | Samples |

| DRV8833CRTER     | ACTIVE | WQFN         | RTE     | 16   | 3000    | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | 8833C          | Samples |

| DRV8833CRTET     | ACTIVE | WQFN         | RTE     | 16   | 250     | Green (RoHS<br>& no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR | -40 to 85    | 8833C          | Samples |

12-Feb-2015

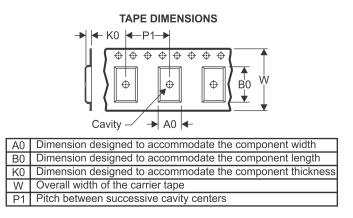

## TAPE AND REEL INFORMATION

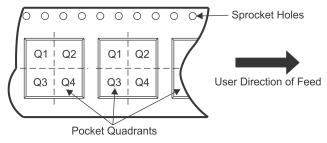

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |                 |                    |    |      |                          |                          |            |            |            |            |           |                  |

|-----------------------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| Device                      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

| DRV8833CPWPR                | HTSSOP          | PWP                | 16 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| DRV8833CRTER                | WQFN            | RTE                | 16 | 3000 | 330.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

| DRV8833CRTET                | WQFN            | RTE                | 16 | 250  | 180.0                    | 12.4                     | 3.3        | 3.3        | 1.1        | 8.0        | 12.0      | Q2               |

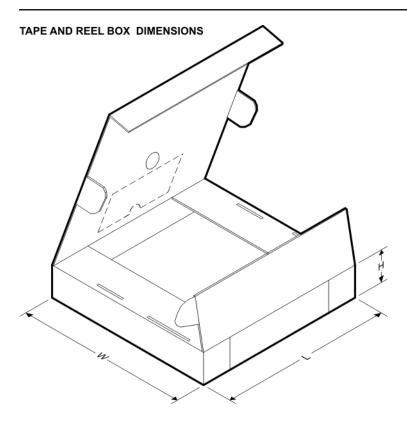

## PACKAGE MATERIALS INFORMATION

12-Feb-2015

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| DRV8833CPWPR | HTSSOP       | PWP             | 16   | 2000 | 367.0       | 367.0      | 35.0        |

| DRV8833CRTER | WQFN         | RTE             | 16   | 3000 | 367.0       | 367.0      | 35.0        |

| DRV8833CRTET | WQFN         | RTE             | 16   | 250  | 210.0       | 185.0      | 35.0        |

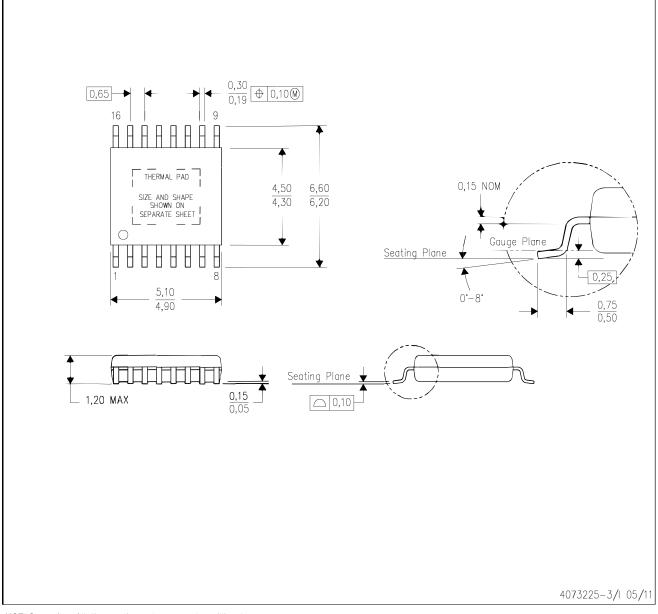

PWP (R-PDSO-G16)

PowerPAD<sup>™</sup> PLASTIC SMALL OUTLINE

NOTES: A. All linear dimensions are in millimeters.

- This drawing is subject to change without notice. Β.

- Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side. C.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad D. This plottage is designed to be soldered to a distinuit ped on the board. Note to resince biol, Forein and Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>.

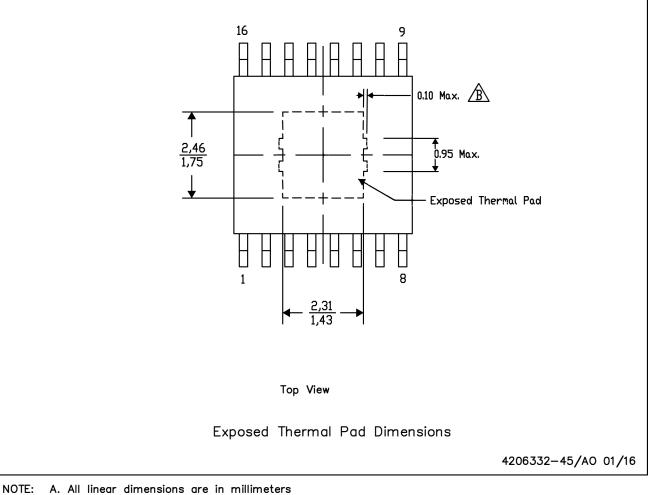

E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- E. Falls within JEDEC MO-153

# PWP (R-PDSO-G16) PowerPAD<sup>™</sup> SMALL PLASTIC OUTLINE

#### THERMAL INFORMATION

This PowerPAD<sup>™</sup> package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

A Exposed tie strap features may not be present.

## **MECHANICAL DATA**

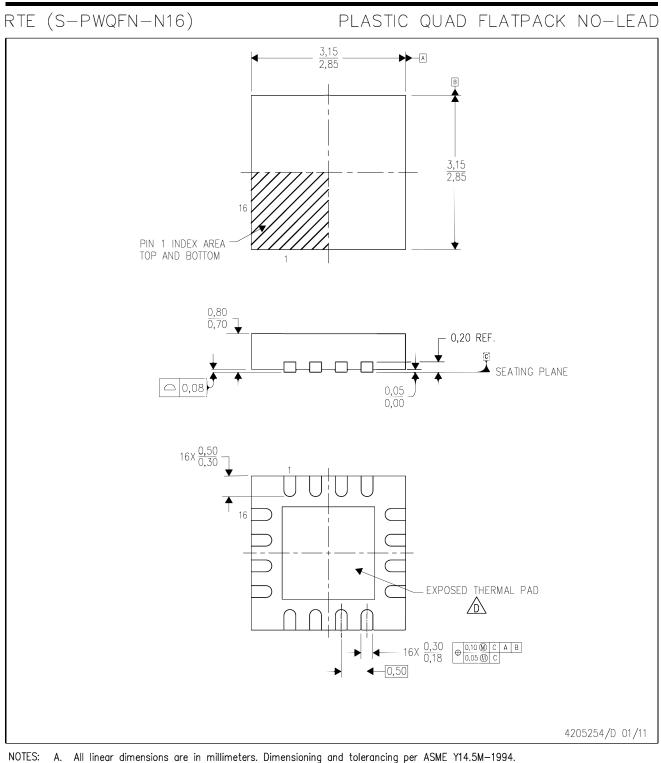

A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.B. This drawing is subject to change without notice.

- C. Quad Flatpack, No-leads (QFN) package configuration.

- The package thermal pad must be soldered to the board for thermal and mechanical performance. See the Product Data Sheet for details regarding the exposed thermal pad dimensions. ∕∆

- E. Falls within JEDEC MO-220.

## RTE (S-PWQFN-N16) PLASTIC QUAD FLATPACK NO-LEAD

## THERMAL INFORMATION

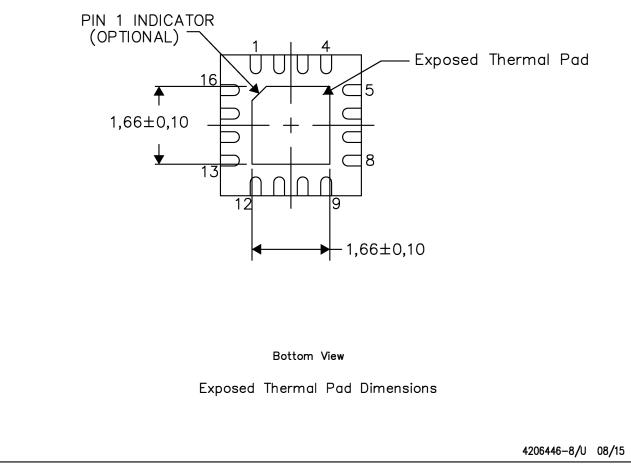

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No-Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

# RTE (S-PWQFN-N16) PLASTIC QUAD FLATPACK NO-LEAD

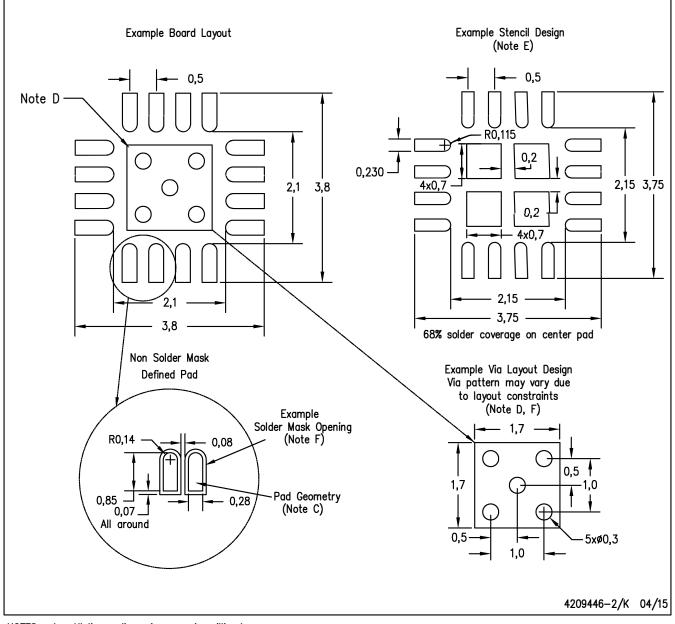

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, Quad Flat—Pack Packages, Texas Instruments Literature No. SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- F. Customers should contact their board fabrication site for minimum solder mask web tolerances between signal pads.