# 500mA, Low Dropout, Low Noise, Ultra-Fast Linear Regulator

### **General Description**

The RT9065 is designed for portable RF and wireless applications with demanding performance and space requirements. The RT9065 performance is optimized for battery powered systems to deliver ultra low noise and low quiescent current. A noise bypass pin is available for further reduction of output noise. Regulator ground current increases only slightly in dropout, further prolonging the battery life. The RT9065 also works with low-ESR ceramic capacitors, reducing the amount of board space necessary for power applications, critical in hand held wireless devices. The RT9065 consumes less than  $0.01\mu A$  in shutdown mode. The other features include low dropout voltage, high output accuracy, current limiting protection, and high ripple rejection ratio. The RT9065 is available in the SOT-23-6 package.

### **Ordering Information**

RT9065 Package Type

E: SOT-23-6

Lead Plating System

G: Green (Halogen Free and Pb Free)

#### Note:

Richtek products are:

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ▶ Suitable for use in SnPb or Pb-free soldering processes.

### **Features**

- Ultra-Low-Noise for RF Application

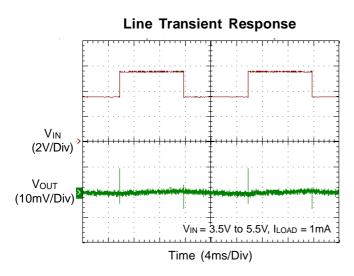

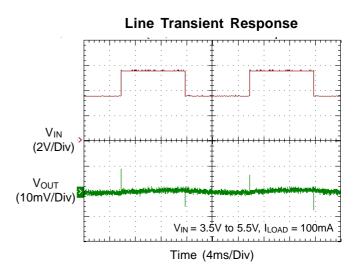

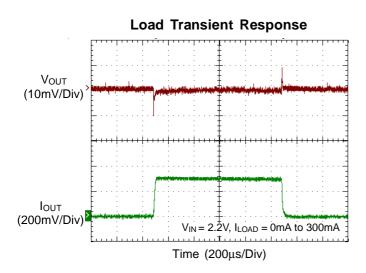

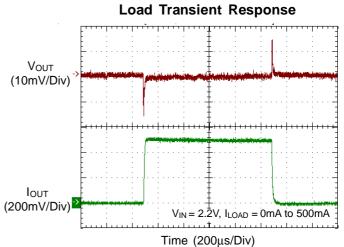

- Ultra-Fast Response in Line/Load Transient

- 0.01µA Shutdown Current

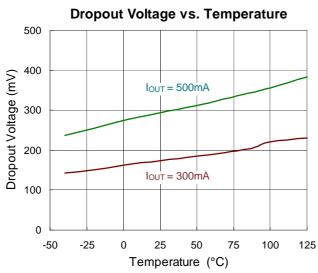

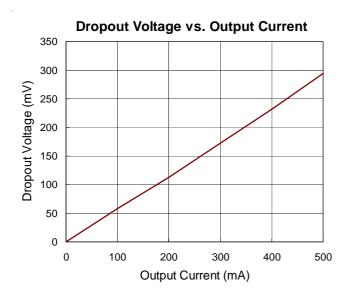

- Low Dropout: 370mV @ 500mA

- Wide Input Voltage Range: 2.2V to 5.5V

- Adjustable Output Voltage

- TTL Logic Controlled Shutdown Input

- Low Temperature Coefficient

- Current Limiting Protection

- Thermal Shutdown Protection

- Only 1µF Output Capacitor Required for Stability

- High Power Supply Rejection Ratio

- RoHS Compliant and Halogen Free

### **Applications**

- CDMA/GSM Cellular Handsets

- Battery Powered Equipment

- Laptop, Palmtops, Notebook Computers

- Hand Held Instruments

- PCMCIA Cards

- Portable Information Appliances

## **Marking Information**

0B=DNN

0B= : Product Code DNN : Date Code

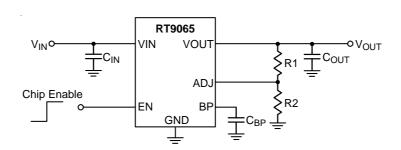

## **Simplified Application Circuit**

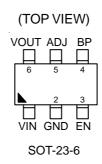

# **Pin Configuration**

# **Functional Pin Description**

| Pin No. | Pin Name | Pin Function                                                                                                                                                            |  |  |  |  |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1       | VIN      | Power input.                                                                                                                                                            |  |  |  |  |

| 2       | GND      | Ground.                                                                                                                                                                 |  |  |  |  |

| 3       | EN       | Chip enable (active high). Note that this pin is high impedance. There should be a pull-low $100k\Omega$ resistor connected to GND when the control signal is floating. |  |  |  |  |

| 4       | BP       | Reference noise bypass.                                                                                                                                                 |  |  |  |  |

| 5       | ADJ      | Feedback input. Connect a resistive divider to adjust the output voltage.                                                                                               |  |  |  |  |

| 6       | VOUT     | Output of the regulator.                                                                                                                                                |  |  |  |  |

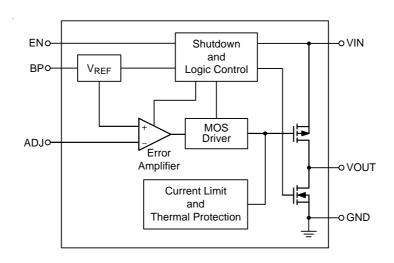

# **Functional Block Diagram**

### **Operation**

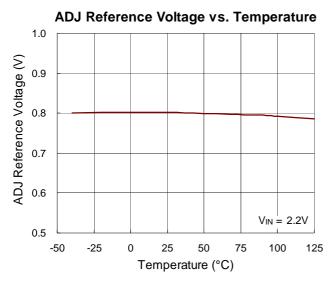

The RT9065 is a low dropout voltage linear regulator designed for RF and wireless applications which require low noise and high PSRR performance. The RT9065 builds in a P-type P-MOSFET with current capability up to 500mA. In normal operation, the Error Amplifier adjusts the gate voltage of the power MOSFET to regulate the ADJ voltage being equal to the internal 0.8V reference voltage.

P-MOSFET current is detected and current limit function will work to limit the output current to a designed value when short circuit happens. Furthermore, the P-MOSFET will be shutdown if the junction temperature is higher than typically 165°C, and released to normal operation until the temperature falls below typically 135°C.

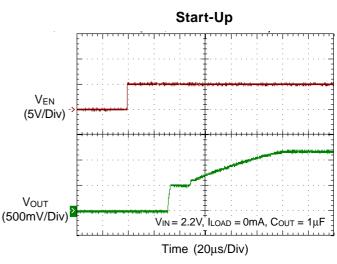

#### Start-Up

This function is defined as chip start up time which is from  $V_{\text{EN}} > V_{\text{IH}}$  to the 95% of  $V_{\text{OUT}}$ .

#### **Shutdown and Logic Control**

This function block includes chip Enable/Disable and UVLO circuits. When chip is disabled, VOUT is pulled to GND through the auto-discharge MOSFET.

# **RT9065**

## Absolute Maximum Ratings (Note 1)

| • Supply Voltage, VIN                                                       | 0.3V to 6V    |

|-----------------------------------------------------------------------------|---------------|

| Chip Enable Input Voltage, EN                                               | 0.3V to 6V    |

| Output Voltage, VOUT                                                        | 0.3V to 6V    |

| • Adjust Output, ADJ                                                        | - −0.3V to 6V |

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |               |

| SOT-23-6                                                                    | - 0.48W       |

| Package Thermal Resistance (Note 2)                                         |               |

| SOT-23-6, θ <sub>JA</sub>                                                   | - 208.2°C/W   |

| • Lead Temperature (Soldering, 10 sec.)                                     | - 260°C       |

| Storage Temperature Range                                                   | 65°C to 150°C |

| • Junction Temperature                                                      | - 150°C       |

| • ESD Susceptibility (Note 3)                                               |               |

| HBM (Human Body Model)                                                      |               |

| MM (Machine Model)                                                          | - 200V        |

|                                                                             |               |

| Recommended Operating Conditions (Note 4)                                   |               |

## **Electrical Characteristics**

$(V_{IN} = V_{OUT} + 1V, C_{IN} = 2.2\mu F, C_{OUT} = 1\mu F, C_{BP} = 22nF, T_A = 25^{\circ}C, unless otherwise specified)$

| Parameter             |            | Symbol            | Test Conditions                                     | Min   | Тур  | Max   | Unit |  |

|-----------------------|------------|-------------------|-----------------------------------------------------|-------|------|-------|------|--|

| ADJ Reference Voltage |            | VADJ              | V <sub>IN</sub> = 5V, I <sub>OUT</sub> = 100mA      | 0.788 | 8.0  | 0.812 | ٧    |  |

| Shutdown Current      |            | Ishdn             | V <sub>EN</sub> = GND                               |       | 0.01 | 1     | μΑ   |  |

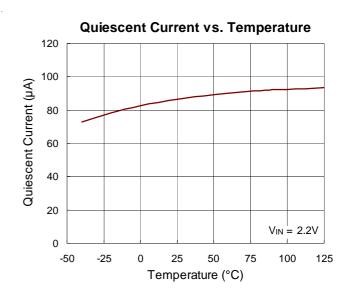

| Quiescent Current     |            | IQ                | I <sub>OUT</sub> = 0mA                              |       | 90   | 120   | μΑ   |  |

| Dropout Voltage       |            | V                 | I <sub>OUT</sub> = 300mA                            |       | 220  | 300   | m)/  |  |

|                       |            | V <sub>DROP</sub> | I <sub>OUT</sub> = 500mA                            |       | 370  | 500   | mV   |  |

| Line Regulation       |            | $\Delta V_{LINE}$ | $V_{IN} = (V_{OUT} + 1V)$ to 5.5V, $I_{OUT} = 1$ mA |       |      | 0.3   | %    |  |

| Load Regulation       |            | $\Delta V_{LOAD}$ | 1mA < I <sub>OUT</sub> < 500mA                      |       |      | 0.6   | %    |  |

| EN Input Bias Current |            | I <sub>IBSD</sub> | VEN = GND or VIN                                    |       | 0    | 100   | nA   |  |

| EN Input              | Logic-High | ViH               |                                                     | 1.2   |      |       | \/   |  |

| Voltage               | Logic-Low  | VIL               |                                                     |       |      | 0.4   | V    |  |

| Parameter                           | Symbol           |                                                                                      | Test Conditions                                                                                                                                          | Min | Тур  | Max | Unit  |

|-------------------------------------|------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

|                                     | tstart           | From V <sub>EN</sub> > V <sub>IH</sub> to V <sub>OUT</sub> = 95% of V <sub>OUT</sub> | $\begin{aligned} V_{IN} &= 3.3 V, \ V_{OUT} = 1.8 V, \\ C_{OUT} &= 10 \mu F \end{aligned}$                                                               | 35  | 60   | 80  | μs    |

|                                     |                  |                                                                                      | $\begin{aligned} V_{IN} &= 3.3 \text{V}, \ V_{OUT} = 1.8 \text{V}, \\ C_{OUT} &= 20 \mu \text{F} \end{aligned}$                                          | 60  | 80   | 120 |       |

| Start-Up Time                       |                  |                                                                                      | $\begin{aligned} \text{V}_{\text{IN}} &= 3.3 \text{V},  \text{V}_{\text{OUT}} = 2.9 \text{V}, \\ \text{C}_{\text{OUT}} &= 30 \mu \text{F} \end{aligned}$ | 130 | 175  | 240 |       |

| Start of Time                       |                  |                                                                                      | $\begin{aligned} \text{V}_{\text{IN}} &= 3.3 \text{V},  \text{V}_{\text{OUT}} = 2.9 \text{V}, \\ \text{C}_{\text{OUT}} &= 60 \mu \text{F} \end{aligned}$ | 250 | 340  | 450 |       |

|                                     |                  |                                                                                      | $\begin{aligned} \text{V}_{\text{IN}} &= 5\text{V},  \text{V}_{\text{OUT}} = 3.3\text{V}, \\ \text{C}_{\text{OUT}} &= 30\mu\text{F} \end{aligned}$       | 140 | 180  | 250 |       |

|                                     |                  |                                                                                      | V <sub>IN</sub> = 5V, V <sub>OUT</sub> = 3.3V,<br>C <sub>OUT</sub> = 60μF                                                                                | 270 | 350  | 480 |       |

|                                     | tEN_Delay        | From V <sub>EN</sub> > V <sub>IH</sub> to V <sub>OUT</sub> = 0% of V <sub>OUT</sub>  | $\begin{aligned} V_{IN} &= 3.3 V, \ V_{OUT} = 1.8 V, \\ C_{OUT} &= 10 \mu F \end{aligned}$                                                               | 5   | 15   | 30  | - μs  |

|                                     |                  |                                                                                      | $\begin{aligned} V_{IN} &= 3.3 V, \ V_{OUT} = 1.8 V, \\ C_{OUT} &= 20 \mu F \end{aligned}$                                                               | 5   | 15   | 30  |       |

| EN Start Up Dolay Time              |                  |                                                                                      | $V_{IN}=3.3V,V_{OUT}=2.9V,$ $C_{OUT}=30\mu F$                                                                                                            | 5   | 15   | 30  |       |

| EN Start-Up Delay Time              |                  |                                                                                      | $\begin{aligned} \text{V}_{\text{IN}} &= 3.3 \text{V},  \text{V}_{\text{OUT}} = 2.9 \text{V}, \\ \text{C}_{\text{OUT}} &= 60 \mu \text{F} \end{aligned}$ | 5   | 15   | 30  |       |

|                                     |                  |                                                                                      | $\begin{aligned} \text{V}_{\text{IN}} &= 5\text{V},  \text{V}_{\text{OUT}} = 3.3\text{V}, \\ \text{C}_{\text{OUT}} &= 30\mu\text{F} \end{aligned}$       | 5   | 10   | 20  |       |

|                                     |                  |                                                                                      | $\begin{aligned} V_{\text{IN}} &= 5\text{V}, \ V_{\text{OUT}} = 3.3\text{V}, \\ C_{\text{OUT}} &= 60\mu\text{F} \end{aligned}$                           | 5   | 10   | 20  |       |

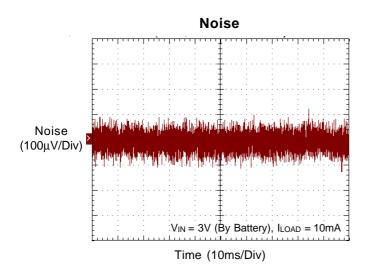

| Output Noise Voltage                | eNO              | 10kHz to 100kHz, $I_{OUT} = 200mA$ , $C_{OUT} = 1\mu F$                              |                                                                                                                                                          |     | 100  | 1   | μVRMS |

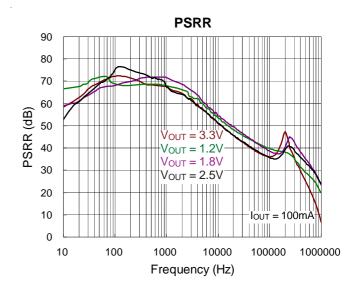

| Power Supply f = 100Hz              | PSRR             | Cour = 1                                                                             | -<br>Ε Ιουτ = 10m Λ                                                                                                                                      |     | 70   |     | dB    |

| Rejection Rate f = 10kHz            | te f = 10kHz     |                                                                                      | $C_{OUT} = 1\mu F$ , $I_{OUT} = 10mA$                                                                                                                    |     | 50   |     | ub    |

| Under Voltage Lockout<br>Threshold  | Vuvlo            | V <sub>IN</sub> Rising                                                               |                                                                                                                                                          | 1.6 | 1.8  | 2   | V     |

| Under Voltage Lockout<br>Hysteresis | ΔVυνιο           |                                                                                      |                                                                                                                                                          | 0.1 | 0.15 |     | V     |

| Current Limit                       | I <sub>LIM</sub> | $R_{LOAD} = 1\Omega$                                                                 |                                                                                                                                                          | 500 | 650  |     | mA    |

| Thermal Shutdown<br>Threshold       | T <sub>SD</sub>  |                                                                                      |                                                                                                                                                          |     | 165  |     | °C    |

| Hysteresis                          | ΔT <sub>SD</sub> |                                                                                      |                                                                                                                                                          |     | 30   |     | °C    |

**Note 1.** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}C$  on a high effective thermal conductivity four-layer test board per JEDEC 51-7.

- Note 3. Devices are ESD sensitive. Handling precaution recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

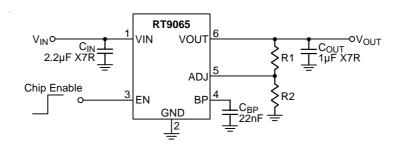

# **Typical Application Circuit**

## **Typical Operating Characteristics**

### **Application Information**

The RT9065 requires input and output decoupling capacitors. These capacitors must be correctly selected for good performance and insufficient decoupling capacitance may cause oscillation.

#### **Input Capacitor**

The value of input capacitor should be  $\geq 2.2 \mu F$ . The input capacitor must be placed within 1cm from the device to assure input stability. There are no requirements for the ESR (equivalent series resistance) on the input capacitor, but low-ESR ceramic capacitor with larger value provides better PSRR and line transient response.

### **Output Capacitor**

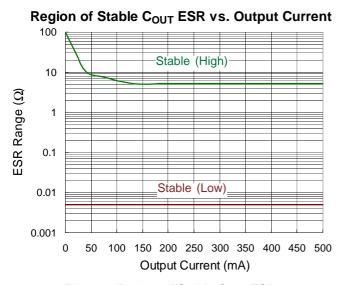

The output capacitor must meet both requirements for minimum amount of capacitance and ESR for the LDO application. The RT9065 is designed specifically to work with low-ESR ceramic output capacitor in consideration of space-saving and performance. To ensure the stability, the value of ceramic capacitor should be at least  $1\mu F$  and ESR should be >  $5m\Omega$ . The RT9065 can also work well with other types of output capacitors. Figure 1 shows the stable range of ESR as a function of load current for various output capacitor values. Output capacitor with larger capacitance can reduce noise and improve load transient response, stability, and PSRR. The output capacitor should be located no more than 0.5 inches from the VOUT pin.

Figure 1. Region of Stable Cout ESR

#### **Adjustable Output Voltage**

The output voltage is set by the ratio of two external resistors as follow:

$$V_{OUT} = 0.8 \times (1 + R1/R2)$$

#### **Bypass Capacitor and Low Noise**

Connecting a 22nF capacitor between the BP pin and the GND pin significantly reduces noise on the regulator output, and it is critical that the capacitor should be placed close to the IC and PCB traces should be as short as possible. DC leakage on this pin can affect the LDO regulator output noise and voltage regulation performance.

#### **Enable Function**

The RT9065 features an enable/disable function. The enable control level must be greater than 1.2V to turn-on the device. When the voltage on the EN pin falls below 0.4V, the LDO will be shut down and will reduce quiescent current to less than  $1\mu A$ . If the enable function is not needed in a specific application, it should be tied to VIN to keep the LDO in a continuously on state.

#### **Current Limit**

The RT9065 contains an independent current limiter, which monitors and controls the pass transistor's gate voltage, limiting the output current to 0.65A (typ.). The output can be shorted to ground without damaging the part.

#### **Thermal Considerations**

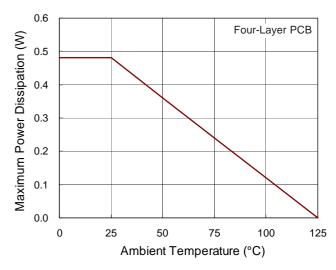

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

## **RT9065**

For recommended operating condition specifications, the maximum junction temperature is 125°C. The junction to SOT-23-6 package, the thermal resistance,  $\theta_{JA}$ , is 208.2°C/W on a standard JEDEC 51-7 four-layer thermal test board. The maximum power dissipation at  $T_A = 25^{\circ}\text{C}$  can be calculated by the following formula :

$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (208.2^{\circ}C/W) = 0.48W$  for SOT-23-6 package

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA}$ . The derating curve in Figure 2 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 2. Derating Curve of Maximum Power Dissipation

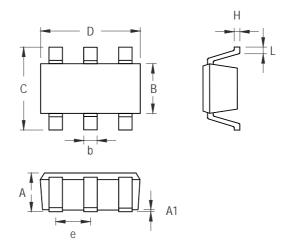

### **Outline Dimension**

| Symbol | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|--------|--------------|---------------|----------------------|-------|--|

|        | Min          | Max           | Min                  | Max   |  |

| Α      | 0.889        | 1.295         | 0.031                | 0.051 |  |

| A1     | 0.000        | 0.152         | 0.000                | 0.006 |  |

| В      | 1.397        | 1.803         | 0.055                | 0.071 |  |

| b      | 0.250        | 0.560         | 0.010                | 0.022 |  |

| С      | 2.591        | 2.997         | 0.102                | 0.118 |  |

| D      | 2.692        | 3.099         | 0.106                | 0.122 |  |

| е      | 0.838        | 1.041         | 0.033                | 0.041 |  |

| Н      | 0.080        | 0.254         | 0.003                | 0.010 |  |

| L      | 0.300        | 0.610         | 0.012                | 0.024 |  |

**SOT-23-6 Surface Mount Package**

### **Richtek Technology Corporation**

5F, No. 20, Taiyuen Street, Chupei City Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

RICHTEK

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

DS9065-03 May 2020 www.richtek.com