## SGM51652H4/SGM51652H8 16-Bit, 500kSPS, 4- and 8-Channel, Single Supply, SAR ADCs with Bipolar Input Ranges

### GENERAL DESCRIPTION

The SGM51652H4 and SGM51652H8 are 4-channel and 8-channel, high-precision successive approximation (SAR) analog-to-digital converter (ADC).

These ADCs are powered by a single unipolar 5V, supports true bipolar ±10.24V, ±5.12V, and ±2.56V inputs, as well as unipolar input ranges of 0V to 10.24V and 0V to 5.12V. The input range is configured by software.

These chips provides over-voltage protection at input, it's up to ±20V.

These chips have an on-chip high accuracy and low drift 10ppm reference.

The input impedance of these chips is  $\geq 1M\Omega$  and it's dependent of input range selection.

The digital interface is compatible to the traditional SPI protocol.

### **FEATURES**

- 16 Bits ADC

- Programmable Input Ranges:

- Bipolar Ranges: ±10.24V, ±5.12V, and ±2.56V

- Unipolar Ranges: 0V to 10.24V and 0V to 5.12V

- Supply Voltage Ranges:

- Analog Supply: 5V

- I/O Supply: 1.65V to 5V

- On-Chip Reference: 4.096V

- Differential Nonlinearity (DNL): ±0.65LSB

- Integral Nonlinearity (INL):

- ±1.1LSB for All Bipolar Ranges

- ±0.5LSB for All Unipolar Ranges

- Signal-to-Noise Ratio (SNR): 91dB

- Total Harmonic Distortion (THD): -102dB

- Alarm Features

- Daisy-Chain Operation

- -40°C to +125°C Operating Temperature Range

- Available in a Green TSSOP-38 Package

### **APPLICATIONS**

PLC Analog Input Modules Power Automation Factory Automation

**Protection Relays**

## 16-Bit, 500kSPS, 4- and 8-Channel, Single Supply, SAR ADCs with Bipolar Input Ranges

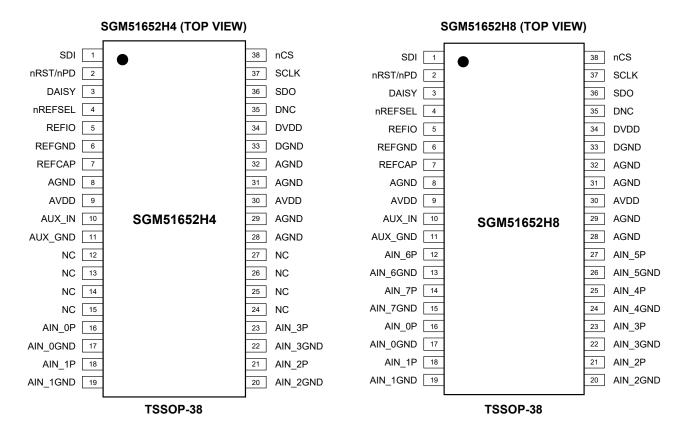

### PIN CONFIGURATIONS

## PIN DESCRIPTION

| PIN | NAME                |            | TYPE (1) | FUNCTION                                                    |  |  |  |  |

|-----|---------------------|------------|----------|-------------------------------------------------------------|--|--|--|--|

| PIN | SGM51652H4          | SGM51652H8 | ITPE     | FONCTION                                                    |  |  |  |  |

| 1   | SI                  | IO         | DI       | Serial Data Input.                                          |  |  |  |  |

| 2   | nRST/nPD            |            | DI       | Dual-Function Pin: Reset/Power-Down the Device. Active low. |  |  |  |  |

| 3   | DAISY               |            | DI       | Chain the Serial Data Input in Daisy-Chain Mode.            |  |  |  |  |

| 4   | nREF                | SEL        | DI       | Active Low. When it's enable, the Internal Reference is on. |  |  |  |  |

| 5   | REFIO               |            | AIO      | Internal Reference Output and External Reference Input Pin. |  |  |  |  |

| 6   | REF                 | GND        | Р        | Reference Ground Pin.                                       |  |  |  |  |

| 7   | REF(                | CAP        | AO       | ADC Reference Decoupling Capacitor Pin.                     |  |  |  |  |

| 8   | AG                  | ND         | Р        | Analog Ground.                                              |  |  |  |  |

| 9   | AVDD P Analog Power |            | Р        | Analog Power Supply.                                        |  |  |  |  |

| 10  | AUX_IN              |            | Al       | Positive Auxiliary Input Pin.                               |  |  |  |  |

| 11  | AUX_                | GND        | Al       | Negative Auxiliary Input Pin.                               |  |  |  |  |

# 16-Bit, 500kSPS, 4- and 8-Channel, Single Supply, SAR ADCs with Bipolar Input Ranges

## **PIN DESCRIPTION (continued)**

| PIN           | NA         | ME         | TYPE (1)          | FUNCTION                                   |

|---------------|------------|------------|-------------------|--------------------------------------------|

| PIN           | SGM51652H4 | SGM51652H8 | ITPE              | FUNCTION                                   |

| 12            | NC         | AIN_6P     | Al                | Channel 6 Positive Analog Input.           |

| 13            | NC         | AIN_6GND   | Al                | Channel 6 Negative Analog Input.           |

| 14            | NC         | AIN_7P     | Al                | Channel 7 Positive Analog Input.           |

| 15            | NC         | AIN_7GND   | Al                | Channel 7 Negative Analog Input.           |

| 16            | AIN        | _0P        | Al                | Channel 0 Positive Analog Input.           |

| 17            | AIN_0      | OGND       | Al                | Channel 0 Negative Analog Input.           |

| 18            | AIN        | _1P        | Al                | Channel 1 Positive Analog Input.           |

| 19            | AIN_       | 1GND       | Al                | Channel 1 Negative Analog Input.           |

| 20            | AIN_2      | 2GND       | Al                | Channel 2 Negative Analog Input.           |

| 21            | AIN        | _2P        | Al                | Channel 2 Positive Analog Input.           |

| 22            | AIN_3GND   |            | Al                | Channel 3 Negative Analog Input.           |

| 23            | AIN        | _3P        | Al                | Channel 3 Positive Analog Input.           |

| 24            | NC         | AIN_4GND   | Al                | Channel 4 Negative Analog Input.           |

| 25            | NC         | AIN_4P     | Al                | Channel 4 Positive Analog Input.           |

| 26            | NC         | AIN_5GND   | Al                | Channel 5 Negative Analog Input            |

| 27            | NC         | AIN_5P     | Al                | Channel 5 Positive Analog Input.           |

| 28, 29,<br>32 | AG         | ND         | Р                 | Analog Ground.                             |

| 30            | AV         | DD         | Р                 | Analog Power Supply.                       |

| 31            | AG         | ND         | Р                 | Analog Ground.                             |

| 33            | DG         | ND         | Р                 | Digital Ground.                            |

| 34            | DV         | DD         | Р                 | Digital Power Supply.                      |

| 35            | DNC        |            | Do Not<br>Connect | Do Not Connect This Pin. Keep it floating. |

| 36            | SE         | 00         | DO                | Serial Data Output.                        |

| 37            | SC         | LK         | DI                | Serial Clock Input.                        |

| 38            | nC         | cs         | DI                | Chip-Select Input Pin. Active low.         |

NOTE: 1. Al = Analog Input, AO = Analog Output, AIO = Analog Input and Output, DI = Digital Input, DO = Digital Output, DIO = Digital Input and Output, P = Power Supply.

# 16-Bit, 500kSPS, 4- and 8-Channel, Single Supply, SAR ADCs with Bipolar Input Ranges

## **ELECTRICAL CHARACTERISTICS**

(AVDD = 5V, DVDD = 3V,  $V_{REF}$  = 4.096V (internal), and  $f_{SAMPLE}$  = 500kSPS, Full = -40°C to +125°C, typical values are at  $T_A$  = +25°C, unless otherwise noted.)

| PARAMETER                                        | SYMBOL               | CONDITIONS                                                                             | MIN                       | TYP                          | MAX                         | UNITS  |

|--------------------------------------------------|----------------------|----------------------------------------------------------------------------------------|---------------------------|------------------------------|-----------------------------|--------|

| Analog Inputs                                    |                      |                                                                                        |                           |                              |                             |        |

|                                                  |                      | Input range = ±2.5 × V <sub>REF</sub>                                                  | -2.5 × V <sub>REF</sub>   |                              | 2.5 × V <sub>REF</sub>      |        |

|                                                  |                      | Input range = ±1.25 × V <sub>REF</sub>                                                 | -1.25 × V <sub>REF</sub>  |                              | 1.25 × V <sub>REF</sub>     |        |

| Full-Scale Input Span (1) (AIN nP to AIN nGND)   |                      | Input range = ±0.625 × V <sub>REF</sub>                                                | -0.625 × V <sub>REF</sub> |                              | 0.625 ×<br>V <sub>REF</sub> | V      |

| . – – ,                                          |                      | Input range = 2.5 × V <sub>REF</sub>                                                   | 0                         |                              | 2.5 × V <sub>REF</sub>      |        |

|                                                  |                      | Input range = 1.25 × V <sub>REF</sub>                                                  | 0                         |                              | 1.25 × V <sub>REF</sub>     |        |

|                                                  |                      | Input range = ±2.5 × V <sub>REF</sub>                                                  | -2.5 × V <sub>REF</sub>   |                              | 2.5 × V <sub>REF</sub>      |        |

|                                                  |                      | Input range = ±1.25 × V <sub>REF</sub>                                                 | -1.25 × V <sub>REF</sub>  |                              | 1.25 × V <sub>REF</sub>     |        |

| Operating Input Range, Positive Input (AIN_nP)   |                      | Input range = ±0.625 × V <sub>REF</sub>                                                | -0.625 × V <sub>REF</sub> |                              | 0.625 ×<br>V <sub>REF</sub> | ٧      |

|                                                  |                      | Input range = 2.5 × V <sub>REF</sub>                                                   | 0                         |                              | 2.5 × V <sub>REF</sub>      |        |

|                                                  |                      | Input range = 1.25 × V <sub>REF</sub>                                                  | 0                         |                              | 1.25 × V <sub>REF</sub>     |        |

| Operating Input Range, Negative Input (AIN_nGND) |                      | All input ranges                                                                       | -0.1                      | 0                            | 0.1                         | >      |

| Input Impedance                                  | Z <sub>I</sub>       | At T <sub>A</sub> = +25°C, all input ranges                                            | 0.85                      | 1                            | 1.15                        | ΜΩ     |

| Input Impedance Drift                            |                      | All input ranges                                                                       |                           | 7                            | 25                          | ppm/°C |

|                                                  |                      | With voltage at AIN_nP pin = $V_{IN}$ , input range = $\pm 2.5 \times V_{REF}$         |                           | $\frac{V_{IN}-2.25}{R_{IN}}$ |                             | μΑ     |

|                                                  |                      | With voltage at AIN_nP pin = $V_{IN}$ , input range = $\pm 1.25 \times V_{REF}$        |                           | $\frac{V_{IN}-2.00}{R_{IN}}$ |                             | μA     |

| Input Leakage Current                            | I <sub>Ikg(in)</sub> | With voltage at AIN_nP pin = V <sub>IN</sub> , input range = ±0.625 × V <sub>REF</sub> |                           | $\frac{V_{IN}-1.60}{R_{IN}}$ |                             | μA     |

|                                                  |                      | With voltage at AIN_nP pin = $V_{IN}$ , input range = 2.5 × $V_{REF}$                  |                           | $\frac{V_{IN}-2.50}{R_{IN}}$ |                             | μA     |

|                                                  |                      | With voltage at AIN_nP pin = VIN, input range = 1.25 × V <sub>REF</sub>                |                           | $\frac{V_{IN}-2.50}{R_{IN}}$ |                             | μA     |

| Input Over-Voltage Protection                    |                      |                                                                                        |                           |                              |                             |        |

| Over Veltage Protection Veltage                  | V                    | AVDD = 5V or offers low impedance < 30kΩ, all input ranges                             | -20                       |                              | 20                          | ٧      |

| Over-Voltage Protection Voltage                  | V <sub>OVP</sub>     | AVDD = floating with impedance > 30kΩ, all input ranges                                | -11                       |                              | 11                          | ٧      |

#### NOTE:

1. Ideal input span, does not include gain or offset error.

# 16-Bit, 500kSPS, 4- and 8-Channel, Single Supply, SAR ADCs with Bipolar Input Ranges

## **ELECTRICAL CHARACTERISTICS (continued)**

(AVDD = 5V, DVDD = 3V,  $V_{REF}$  = 4.096V (internal), and  $f_{SAMPLE}$  = 500kSPS, Full = -40°C to +125°C, typical values are at  $T_A$  = +25°C, unless otherwise noted.)

| PARAMETER                                   | SYMBOL            | CONDITIONS                                                            | MIN   | TYP   | MAX      | UNITS    |

|---------------------------------------------|-------------------|-----------------------------------------------------------------------|-------|-------|----------|----------|

| System Performance                          | •                 |                                                                       | •     | •     | <u>'</u> | •        |

| Resolution                                  |                   |                                                                       | 16    |       |          | Bits     |

| No Missing Codes                            | NMC               |                                                                       | 16    |       |          | Bits     |

| Differential Nonlinearity                   | DNL               |                                                                       | -0.99 | ±0.5  | 1.5      | LSB (2)  |

| Integral Nonlinearity (3)                   | INL               |                                                                       | -2    | ±0.75 | 2        | LSB      |

| Gain Error                                  | E <sub>G</sub>    | At T <sub>A</sub> = +25°C, all input ranges                           |       | ±0.02 | ±0.05    | %FSR (4) |

| Gain Error Matching<br>(Channel-to-Channel) |                   | At T <sub>A</sub> = +25°C, all input ranges                           |       | ±0.02 | ±0.05    | %FSR     |

| Gain Error Temperature Drift                |                   | All input ranges                                                      |       | ±1    | ±4       | ppm/°C   |

|                                             |                   | At $T_A = +25$ °C,<br>input range = $\pm 2.5 \times V_{REF}$          |       | ±0.5  | ±0.75    |          |

|                                             |                   | At $T_A = +25$ °C,<br>input range = ±1.25 × $V_{REF}$                 |       | ±0.5  | ±1       |          |

| Offset Error                                | Eo                | At $T_A = +25$ °C,<br>input range = ±0.625 × $V_{REF}$                |       | ±0.5  | ±1.5     | mV       |

|                                             |                   | At $T_A = +25$ °C,<br>input range = 0 to 2.5 × $V_{REF}$              |       | ±0.5  | ±2       |          |

|                                             |                   | At $T_A = +25$ °C,<br>input range = 0 to 1.25 × $V_{REF}$             |       | ±0.5  | ±2       |          |

|                                             |                   | At $T_A = +25^{\circ}C$ ,<br>input range = $\pm 2.5 \times V_{REF}$   |       | ±0.5  | ±0.75    |          |

|                                             |                   | At $T_A = +25^{\circ}C$ ,<br>input range = $\pm 1.25 \times V_{REF}$  |       | ±0.5  | ±1       |          |

| Offset Error Matching (Channel-to-Channel)  |                   | At $T_A = +25^{\circ}C$ ,<br>input range = $\pm 0.625 \times V_{REF}$ |       | ±0.5  | ±1.5     | mV       |

|                                             |                   | At $T_A = +25$ °C,<br>input range = 0 to 2.5 × $V_{REF}$              |       | ±0.5  | ±2       |          |

|                                             |                   | At $T_A = +25$ °C,<br>input range = 0 to 1.25 × $V_{REF}$             |       | ±0.5  | ±2       |          |

| Offset Error Temperature Drift              |                   | All input ranges                                                      |       | ±1    | ±3       | ppm/°C   |

| Sampling Dynamics                           |                   |                                                                       |       |       |          |          |

| Conversion Time                             | t <sub>CONV</sub> |                                                                       |       |       | 850      | ns       |

| Acquisition Time                            | t <sub>ACQ</sub>  |                                                                       | 1150  |       |          | ns       |

| Maximum Throughput Rate without Latency     | fs                |                                                                       |       |       | 500      | kSPS     |

#### NOTES:

- 2. LSB = least significant bit.

- 3. This parameter is the endpoint INL, not best fit INL.

- 4. FSR = full-scale range.

# 16-Bit, 500kSPS, 4- and 8-Channel, Single Supply, SAR ADCs with Bipolar Input Ranges

## **ELECTRICAL CHARACTERISTICS (continued)**

(AVDD = 5V, DVDD = 3V,  $V_{REF}$  = 4.096V (internal), and  $f_{SAMPLE}$  = 500kSPS, Full = -40°C to +125°C, typical values are at  $T_A$  = +25°C, unless otherwise noted.)

| PARAMETER                                                      | 1      | SYMBOL                                                         | CONDITIONS                                                         | MIN   | TYP   | MAX       | UNITS |

|----------------------------------------------------------------|--------|----------------------------------------------------------------|--------------------------------------------------------------------|-------|-------|-----------|-------|

| Dynamic Characteristics                                        | i      |                                                                |                                                                    |       |       |           |       |

|                                                                |        |                                                                | Input range = ±2.5 × V <sub>REF</sub>                              | 90    | 92    |           |       |

|                                                                |        |                                                                | Input range = ±1.25 × V <sub>REF</sub>                             | 89    | 91    |           |       |

| Signal-to-Noise Ratio<br>(V <sub>IN</sub> - 0.5dBFS at 1kHz)   |        | SNR                                                            | Input range = ±0.625 × V <sub>REF</sub>                            | 87.5  | 89    |           | dB    |

| ,                                                              |        |                                                                | Input range = 2.5 × V <sub>REF</sub>                               | 88.5  | 90.5  |           |       |

|                                                                |        |                                                                | Input range = 1.25 × V <sub>REF</sub>                              | 87.5  | 89    |           |       |

| Total Harmonic Distortion (V <sub>IN</sub> - 0.5dBFS at 1kHz)  | (5)    | THD                                                            | All input ranges                                                   |       | -102  |           | dB    |

| ,                                                              |        |                                                                | Input range = ±2.5 × V <sub>REF</sub>                              | 89    | 91.5  |           |       |

|                                                                |        |                                                                | Input range = ±1.25 × V <sub>REF</sub>                             | 88.5  | 91    |           |       |

| Signal-to-Noise Ratio<br>(V <sub>IN</sub> - 0.5dBFS at 1kHz)   |        | SINAD                                                          | Input range = ±0.625 × V <sub>REF</sub>                            | 87    | 89    |           | dB    |

| (VIN 0.0db) out iniz)                                          |        |                                                                | Input range = 2.5 × V <sub>REF</sub>                               | 87.5  | 90.5  |           |       |

|                                                                |        |                                                                | Input range = 1.25 × V <sub>REF</sub>                              | 87    | 89    |           |       |

| Spurious-Free Dynamic R<br>(V <sub>IN</sub> - 0.5dBFS at 1kHz) | ange   | SFDR                                                           | All input ranges                                                   |       | 103   |           | dB    |

| Crosstalk Isolation (6)                                        |        |                                                                | Aggressor channel input is overdriven to 2 × maximum input voltage |       | 110   |           | dB    |

| Crosstalk Memory (7)                                           |        |                                                                | Aggressor channel input is overdriven to 2 × maximum input voltage |       | 90    |           | dB    |

| Consult Cinneral Dansdavidth                                   | -3dB   | BW <sub>-3dB</sub> At T <sub>A</sub> = +25°C, all input ranges |                                                                    |       | 15    |           | kHz   |

| Small-Signal Bandwidth                                         | -0.1dB | BW <sub>-0.1dB</sub>                                           | BW <sub>-0.1dB</sub> At $T_A = +25^{\circ}C$ , all input ranges    |       | 2.5   |           | kHz   |

| Auxiliary Channel                                              |        |                                                                |                                                                    |       |       |           |       |

| Resolution                                                     |        |                                                                |                                                                    | 16    |       |           | Bits  |

| AUX_IN Voltage Range                                           |        | $V_{AUX\_IN}$                                                  | AUX_IN - AUX_GND                                                   | 0     |       | $V_{REF}$ | V     |

| Operating Input Range                                          |        |                                                                | AUX_IN                                                             | 0     |       | $V_{REF}$ | V     |

| Operating input Nange                                          |        |                                                                | AUX_GND                                                            |       | 0     |           | V     |

| Input Capacitance                                              |        | Cı                                                             | During sampling                                                    |       | 75    |           | pF    |

| input Capacitance                                              |        | O                                                              | During conversion                                                  |       | 5     |           | рі    |

| Input Leakage Current                                          |        | I <sub>Ikg(in)</sub>                                           |                                                                    |       | 100   |           | nA    |

| Differential Nonlinearity                                      |        | DNL                                                            |                                                                    | -0.99 | ±0.6  | 1.5       | LSB   |

| Integral Nonlinearity                                          |        | INL                                                            |                                                                    | -4    | ±1.5  | 4         | LSB   |

| Gain Error                                                     |        | $E_{G(AUX)}$                                                   | At $T_A = +25$ °C                                                  |       | ±0.02 | ±0.2      | % FSR |

| Offset Error                                                   |        | E <sub>O(AUX)</sub>                                            | At T <sub>A</sub> = +25°C                                          | -10   |       | 10        | mV    |

| Signal-to-Noise Ratio S                                        |        | SNR                                                            | V <sub>AUX_IN</sub> = -0.5dBFS at 1kHz                             | 87    | 89    |           | dB    |

| Total Harmonic Distortion                                      | (5)    | THD                                                            | V <sub>AUX_IN</sub> = -0.5dBFS at 1kHz                             |       | -102  |           | dB    |

| Signal-to-Noise + Distortio                                    | n      | SINAD                                                          | V <sub>AUX_IN</sub> = -0.5dBFS at 1kHz                             | 86    | 88.5  |           | dB    |

| Spurious-Free Dynamic R                                        | ange   | SFDR                                                           | V <sub>AUX_IN</sub> = -0.5dBFS at 1kHz                             |       | 103   |           | dB    |

#### NOTES:

- 5. Accumulated the first nine harmonics.

- 6. Any off-channel with 10 kHz, Full-scale sinusoidal input to channel being sampled with DC input.

- 7. From previously sampled to channel with 10kHz, Full-scale sinusoidal input to channel being sampled with DC input.

# 16-Bit, 500kSPS, 4- and 8-Channel, Single Supply, SAR ADCs with Bipolar Input Ranges

## **ELECTRICAL CHARACTERISTICS (continued)**

(AVDD = 5V, DVDD = 3V,  $V_{REF}$  = 4.096V (internal), and  $f_{SAMPLE}$  = 500kSPS, Full = -40°C to +125°C, typical values are at  $T_A$  = +25°C, unless otherwise noted.)

| PARA                                     | METER                  | SYMBOL                  | CONDITION                                                 | IS                    | MIN           | TYP   | MAX           | UNITS  |

|------------------------------------------|------------------------|-------------------------|-----------------------------------------------------------|-----------------------|---------------|-------|---------------|--------|

| Internal Refere                          | nce Output             |                         |                                                           |                       |               |       |               |        |

| Voltage on REFI<br>(Configured as 0      | Output) <sup>(8)</sup> | $V_{REFIO\_INT}$        | At T <sub>A</sub> = +25°C                                 |                       | 4.095         | 4.096 | 4.097         | V      |

| Internal Referen<br>Drift                | ce Temperature         |                         |                                                           |                       |               | 6     | 10            | ppm/°C |

| Decoupling Cap                           | acitor on REFIO        | C <sub>OUT_REFIO</sub>  |                                                           |                       | 10            | 22    |               | μF     |

| Reference voltage to ADC (on REFCAP pin) |                        | V <sub>REFCAP</sub>     | At T <sub>A</sub> = +25°C                                 |                       | 4.095         | 4.096 | 4.097         | V      |

| Reference Buffer Output Impedance        |                        |                         |                                                           |                       |               | 0.5   | 1             | Ω      |

| Reference Buffe<br>Drift                 | r Temperature          |                         |                                                           |                       |               | 0.6   | 1.5           | ppm/°C |

| Decoupling Cap                           | acitor on REFCAP       | C <sub>OUT_REFCAP</sub> |                                                           |                       | 10            | 22    |               | μF     |

| Turn-On Time                             |                        |                         | C <sub>OUT_REFCAP</sub> = 22µF, C <sub>OUT_REF</sub>      | <sub>:IO</sub> = 22µF |               | 15    |               | ms     |

| External Refere                          | ence Input             |                         |                                                           |                       |               |       |               |        |

| External Referer REFIO (Configu          |                        | V <sub>REFIO_EXT</sub>  |                                                           |                       | 4.046         | 4.096 | 4.146         | V      |

| Power-Supply I                           |                        |                         |                                                           |                       |               |       |               |        |

| Analog Power-S                           | upply Voltage          | AVDD                    | Analog supply                                             |                       | 4.75          | 5     | 5.25          | V      |

| D: "   D                                 |                        | D) (DD                  | Digital supply range                                      | 1.65                  | 3.3           | AVDD  | V             |        |

| Digital Power-Su                         | ipply Voltage          | DVDD                    | Digital supply range for specified performance            |                       | 2.7           | 3.3   | 5.25          | V      |

|                                          | Dynamic, AVDD          | I                       | AVDD = 5V, f <sub>S</sub> = maximum                       | SGM51652H8            |               | 13    | 16            | mA     |

|                                          | Dynamic, AVDD          | I <sub>AVDD_DYN</sub>   | and internal reference                                    | SGM51652H4            |               | 8.5   | 11.5          | mA     |

| Analog Supply                            | Static                 |                         | AVDD = 5V, device not converting and internal             | SGM51652H8            |               | 10    | 12            | mA     |

| Current                                  | Static                 | I <sub>AVDD_STC</sub>   | reference                                                 | SGM51652H4            |               | 5.5   | 8.5           | mA     |

|                                          | Standby                | I <sub>STDBY</sub>      | At AVDD = 5V, device in STDBY mode and internal reference |                       |               | 3     | 4.5           | mA     |

|                                          | Power-Down             | I <sub>PWR_DN</sub>     | At AVDD = 5V, device in PW                                | /R_DN                 |               | 3     | 20            | μA     |

| Digital Supply C                         | urrent                 | I <sub>DVDD_DYN</sub>   | At DVDD = 3.3V, output = 0                                | 000h                  |               | 0.5   |               | mA     |

| Digital Inputs (                         | CMOS)                  |                         |                                                           |                       |               |       | •             |        |

| Digital Input Log                        | ic Levels DVDD >       | V <sub>IH</sub>         |                                                           |                       | 0.7 ×<br>DVDD |       | DVDD + 0.3    | V      |

| 2.1V                                     |                        | $V_{IL}$                |                                                           |                       | -0.3          |       | 0.3 ×<br>DVDD | V      |

|                                          | ic Levels DVDD ≤       | V <sub>IH</sub>         |                                                           |                       | 0.8 ×<br>DVDD |       | DVDD +<br>0.3 | V      |

| 2.1V                                     |                        | $V_{IL}$                |                                                           |                       | -0.3          |       | 0.2 ×<br>DVDD | V      |

| Input Leakage C                          | urrent                 |                         |                                                           |                       |               | 100   |               | nA     |

| Input Pin Capacitance                    |                        |                         |                                                           |                       |               | 5     |               | pF     |

| <b>Digital Outputs</b>                   | (CMOS)                 |                         |                                                           |                       |               |       |               |        |

| Digital Output L                         | ogia Lovols            | $V_{OH}$                | I <sub>O</sub> = 500μA source                             |                       | 0.8 ×<br>DVDD |       | DVDD          | V      |

| Digital Output Lo                        |                        | V <sub>OL</sub>         | I <sub>O</sub> = 500μA sink                               |                       | 0             |       | 0.2 ×<br>DVDD | V      |

| Floating State Le                        | eakage                 |                         | Only for SDO                                              |                       |               | 1     |               | μA     |

| Internal Pin Cap                         | acitance               |                         |                                                           |                       | <u> </u>      | 5     |               | pF     |

#### NOTE:

8. Does not consider soldering shift effects.

# 16-Bit, 500kSPS, 4- and 8-Channel, Single Supply, SAR ADCs with Bipolar Input Ranges

## **TIMING REQUIREMENTS: SERIAL INTERFACE**

(AVDD = 5V, DVDD = 3V,  $V_{REF}$  = 4.096V (internal), SDO load = 20pF, and  $f_{SAMPLE}$  = 500kSPS, Full = -40°C to +125°C, typical values are at  $T_A$  = +25°C, unless otherwise noted.)

| PARAMETER                                                 | SYMBOL                | CONDITIONS | MIN                 | TYP | MAX  | UNITS             |

|-----------------------------------------------------------|-----------------------|------------|---------------------|-----|------|-------------------|

| Timing Specifications                                     |                       |            |                     |     |      |                   |

| Sampling Frequency (f <sub>CLK</sub> = max)               | f <sub>S</sub>        |            |                     |     | 500  | kSPS              |

| ADC Cycle Time Period (f <sub>CLK</sub> = max)            | ts                    |            | 2                   |     |      | μs                |

| Serial Clock Frequency (f <sub>S</sub> = max)             | f <sub>SCLK</sub>     |            |                     |     | 66.6 | MHz               |

| Serial Clock Time Period (f <sub>S</sub> = max)           | t <sub>SCLK</sub>     |            | 1/f <sub>SCLK</sub> |     |      | ns                |

| Conversion Time                                           | t <sub>CONV</sub>     |            |                     |     | 850  | ns                |

| Delay Time: nCS Falling to Data Enable                    | t <sub>DZ_CSDO</sub>  |            |                     |     | 10   | ns                |

| Delay Time: Last SCLK Falling to nCS Rising               | t <sub>D_CKCS</sub>   |            | 10                  |     |      | ns                |

| Delay Time: nCS Rising to SDO Going to 3-State            | t <sub>DZ_CSDO</sub>  |            | 10                  |     |      | ns                |

| Timing Requirements                                       |                       |            |                     |     |      |                   |

| Acquisition Time                                          | t <sub>ACQ</sub>      |            | 1150                |     |      | ns                |

| Clock High Time                                           | t <sub>PH_CK</sub>    |            | 0.4                 |     | 0.6  | t <sub>SCLK</sub> |

| Clock Low Time                                            | t <sub>PL_CK</sub>    |            | 0.4                 |     | 0.6  | t <sub>SCLK</sub> |

| nCS High Time                                             | t <sub>PH_CS</sub>    |            | 30                  |     |      | ns                |

| Setup Time: nCS Falling to SCLK Falling                   | t <sub>su_csck</sub>  |            | 30                  |     |      | ns                |

| Hold Time: SCLK Falling to (Previous) Data Valid on SDO   | t <sub>HT_CKDO</sub>  |            | 5                   |     |      | ns                |

| Setup Time: SDO Data Valid to SCLK Falling                | t <sub>SU_DOCK</sub>  |            | 5                   |     |      | ns                |

| Setup Time: SDI Data Valid to SCLK Falling                | t <sub>su_DICK</sub>  |            | 5                   |     |      | ns                |

| Hold Time: SCLK Falling to (Previous) Data Valid on SDI   | t <sub>HT_CKDI</sub>  |            | 5                   |     |      | ns                |

| Setup Time: DAISY Data Valid to SCLK Falling              | t <sub>su_dsyck</sub> |            | 5                   |     |      | ns                |

| Hold Time: SCLK Falling to (Previous) Data Valid on DAISY | t <sub>HT_CKDSY</sub> |            | 5                   |     |      | ns                |

# 16-Bit, 500kSPS, 4- and 8-Channel, Single Supply, SAR ADCs with Bipolar Input Ranges

## **REGISTER MAPS**

R/W: Read/Write bit(s) R: Read only bit(s)

The internal registers are divided into two categories: command registers and program registers.

## **Command Register Description**

Table 1. Command Register Map

| <b>5</b>                                |     |     |     | MSB | Byte |     |    |    | LSB Byte  | Command | 0 " 1 11 15                          |

|-----------------------------------------|-----|-----|-----|-----|------|-----|----|----|-----------|---------|--------------------------------------|

| Register                                | B15 | B14 | B13 | B12 | B11  | B10 | В9 | B8 | B[7:0]    | (Hex)   | Operation in Next Frame              |

| Continued Operation (NO_OP)             | 0   | 0   | 0   | 0   | 0    | 0   | 0  | 0  | 0000 0000 | 0000h   | Continue operation in previous mode  |

| Standby (STDBY)                         | 1   | 0   | 0   | 0   | 0    | 0   | 1  | 0  | 0000 0000 | 8200h   | Device is placed into standby mode   |

| Power-Down (PWR_DN)                     | 1   | 0   | 0   | 0   | 0    | 0   | 1  | 1  | 0000 0000 | 8300h   | Device is powered down               |

| Reset Program Registers (RST)           | 1   | 0   | 0   | 0   | 0    | 1   | 0  | 1  | 0000 0000 | 8500h   | Program register is reset to default |

| Auto Ch. Sequence with Reset (AUTO_RST) | 1   | 0   | 1   | 0   | 0    | 0   | 0  | 0  | 0000 0000 | A000h   | Auto mode enabled following a reset  |

| Manual Ch 0 Selection (MAN_Ch_0)        | 1   | 1   | 0   | 0   | 0    | 0   | 0  | 0  | 0000 0000 | C000h   | Channel 0 input is selected          |

| Manual Ch 1 Selection (MAN_Ch_1)        | 1   | 1   | 0   | 0   | 0    | 1   | 0  | 0  | 0000 0000 | C400h   | Channel 1 input is selected          |

| Manual Ch 2 Selection (MAN_Ch_2)        | 1   | 1   | 0   | 0   | 1    | 0   | 0  | 0  | 0000 0000 | C800h   | Channel 2 input is selected          |

| Manual Ch 3 Selection<br>(MAN_Ch_3)     | 1   | 1   | 0   | 0   | 1    | 1   | 0  | 0  | 0000 0000 | CC00h   | Channel 3 input is selected          |

| Manual Ch 4 Selection (MAN_Ch_4) (1)    | 1   | 1   | 0   | 1   | 0    | 0   | 0  | 0  | 0000 0000 | D000h   | Channel 4 input is selected          |

| Manual Ch 5 Selection (MAN_Ch_5) (1)    | 1   | 1   | 0   | 1   | 0    | 1   | 0  | 0  | 0000 0000 | D400h   | Channel 5 input is selected          |

| Manual Ch 6 Selection (MAN_Ch_6) (1)    | 1   | 1   | 0   | 1   | 1    | 0   | 0  | 0  | 0000 0000 | D800h   | Channel 6 input is selected          |

| Manual Ch 7 Selection (MAN_Ch_7) (1)    | 1   | 1   | 0   | 1   | 1    | 1   | 0  | 0  | 0000 0000 | DC00h   | Channel 7 input is selected          |

| Manual AUX Selection (MAN_AUX)          | 1   | 1   | 1   | 0   | 0    | 0   | 0  | 0  | 0000 0000 | E000h   | AUX channel input is selected        |

#### NOTE:

1. The bits or registers are not included in the SGM5152H4.

# 16-Bit, 500kSPS, 4- and 8-Channel, Single Supply, SAR ADCs with Bipolar Input Ranges

## **REGISTER MAPS (continued)**

## **Program Register Description**

Table 2. Program Register Map

| Register                                | Register<br>Address<br>Bits[15:9] | Default<br>Value (1) | Bit 7      | Bit 6      | Bit 5      | Bit 4      | Bit 3                        | Bit 2                        | Bit 1       | Bit 0  |  |  |  |

|-----------------------------------------|-----------------------------------|----------------------|------------|------------|------------|------------|------------------------------|------------------------------|-------------|--------|--|--|--|

| Auto Scan Sequence                      | ing Contro                        |                      |            |            |            |            |                              |                              |             |        |  |  |  |

| AUTO_SEQ_EN                             | 01h                               | FFh                  | CH7_EN (2) | CH6_EN (2) | CH5_EN (2) | CH4_EN (2) | CH3_EN                       | CH2_EN                       | CH1_EN      | CH0_EN |  |  |  |

| Channel<br>Power-Down                   | 02h                               | 00h                  | CH7_PD (2) | CH6_PD (2) | CH5_PD (2) | CH4_PD (2) | CH3_PD                       | CH2_PD                       | CH1_PD      | CH0_PD |  |  |  |

| Device Features Se                      | Device Features Selection Control |                      |            |            |            |            |                              |                              |             |        |  |  |  |

| Feature Select                          | 03h                               | 00h                  | DEV        | [1:0]      | 0          | 0          | 0 SDO [2:0]                  |                              |             |        |  |  |  |

| Range Select Registers                  |                                   |                      |            |            |            |            |                              |                              |             |        |  |  |  |

| Channel 0 Input<br>Range                | 05h                               | 00h                  | 0          | 0          | 0          | 0          | Range Select Channel 0 [3:0] |                              |             |        |  |  |  |

| Channel 1 Input<br>Range                | 06h                               | 00h                  | 0          | 0          | 0          | 0          | Rar                          | nge Select C                 | hannel 1 [3 | :0]    |  |  |  |

| Channel 2 Input<br>Range                | 07h                               | 00h                  | 0          | 0          | 0          | 0          | Rar                          | Range Select Channel 2 [3:0] |             |        |  |  |  |

| Channel 3 Input<br>Range                | 08h                               | 00h                  | 0          | 0          | 0          | 0          | Rar                          | nge Select C                 | hannel 3 [3 | :0]    |  |  |  |

| Channel 4 Input<br>Range <sup>(2)</sup> | 09h                               | 00h                  | 0          | 0          | 0          | 0          | Rar                          | nge Select C                 | hannel 4 [3 | :0]    |  |  |  |

| Channel 5 Input<br>Range <sup>(2)</sup> | 0Ah                               | 00h                  | 0          | 0          | 0          | 0          | Rar                          | nge Select C                 | hannel 5 [3 | :0]    |  |  |  |

| Channel 6 Input<br>Range <sup>(2)</sup> | 0Bh                               | 00h                  | 0          | 0          | 0          | 0          | Rar                          | nge Select C                 | hannel 6 [3 | :0]    |  |  |  |

| Channel 7 Input<br>Range <sup>(2)</sup> | 0Ch                               | 00h                  | 0          | 0          | 0          | 0          | Rar                          | nge Select C                 | hannel 7 [3 | :0]    |  |  |  |

| Command Read Ba                         | ck (Read-O                        | nly)                 |            |            |            |            |                              |                              |             |        |  |  |  |

| Command Read<br>Back                    | 3Fh                               | 00h                  |            |            | CO         | MMAND_WO   | RD [7:0]                     |                              |             |        |  |  |  |

| Input Floating Detec                    | ction and S                       | tatus                |            |            |            |            |                              |                              |             |        |  |  |  |

| INPUT_FLOATING<br>_DETECTION_EN         | 0Dh                               | 00h                  | CH7_EN (2) | CH6_EN (2) | CH5_EN (2) | CH4_EN (2) | CH3_EN                       | CH2_EN                       | CH1_EN      | CH0_EN |  |  |  |

| INPUT_FLOATING<br>_DETECTION_STA<br>TUS | 0Eh                               | 00h                  | CH7_FT (2) | CH6_FT (2) | CH5_FT (2) | CH4_FT (2) | CH3_FT                       | CH2_FT                       | CH1_FT      | CH0_FT |  |  |  |

#### NOTES

- 1. All registers are reset to the default values at power-on or a reset operation.

- 2. The bits or registers are not included in the SGM5152H4.

# 16-Bit, 500kSPS, 4- and 8-Channel, Single Supply, SAR ADCs with Bipolar Input Ranges

## **REGISTER MAPS (continued)**

### **Auto-Scan Sequencing Control Registers**

### Table 3. AUTO\_SEQ\_EN Register Details

| BITS | BIT NAME   | DESCRIPTION                                                                                                                              | COMMENT | TYPE | RESET |

|------|------------|------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|

| D[7] | CH7_EN (1) | Channel 7 Enable 0 = Channel 7 is not selected for sequencing in AUTO_RST mode 1 = Channel 7 is selected for sequencing in AUTO_RST mode |         | R/W  | 1h    |

| D[6] | CH6_EN (1) | Channel 6 Enable 0 = Channel 6 is not selected for sequencing in AUTO_RST mode 1 = Channel 6 is selected for sequencing in AUTO_RST mode |         | R/W  | 1h    |

| D[5] | CH5_EN (1) | Channel 5 Enable 0 = Channel 5 is not selected for sequencing in AUTO_RST mode 1 = Channel 5 is selected for sequencing in AUTO_RST mode |         | R/W  | 1h    |

| D[4] | CH4_EN (1) | Channel 4 Enable 0 = Channel 4 is not selected for sequencing in AUTO_RST mode 1 = Channel 4 is selected for sequencing in AUTO_RST mode |         | R/W  | 1h    |

| D[3] | CH3_EN     | Channel 3 Enable 0 = Channel 3 is not selected for sequencing in AUTO_RST mode 1 = Channel 3 is selected for sequencing in AUTO_RST mode |         | R/W  | 1h    |

| D[2] | CH2_EN     | Channel 2 Enable 0 = Channel 2 is not selected for sequencing in AUTO_RST mode 1 = Channel 2 is selected for sequencing in AUTO_RST mode |         | R/W  | 1h    |

| D[1] | CH1_EN     | Channel 1 Enable 0 = Channel 1 is not selected for sequencing in AUTO_RST mode 1 = Channel 1 is selected for sequencing in AUTO_RST mode |         | R/W  | 1h    |

| D[0] | CH0_EN     | Channel 0 Enable 0 = Channel 0 is not selected for sequencing in AUTO_RST mode 1 = Channel 0 is selected for sequencing in AUTO_RST mode |         | R/W  | 1h    |

#### NOTE:

1. The bits or registers are not included in the SGM5152H4.

# 16-Bit, 500kSPS, 4- and 8-Channel, Single Supply, SAR ADCs with Bipolar Input Ranges

## **REGISTER MAPS (continued)**

### Channel Power-Down Register (Address = 02h)

**Table 4. Channel Power-Down Register Details**

| BITS | BIT NAME              | DESCRIPTION                                                        | COMMENT | TYPE | RESET |

|------|-----------------------|--------------------------------------------------------------------|---------|------|-------|

| D[7] | CH7_PD (1)            | Channel 7 Power-Down 0 = channel is on 1 = channel is power down   |         | R/W  | 0h    |

| D[6] | CH6_PD (1)            | Channel 6 Power-Down 0 = channel is on 1 = channel is power down   |         | R/W  | 0h    |

| D[5] | CH5_PD (1)            | Channel 5 Power-Down 0 = channel is on 1 = channel is power down   |         | R/W  | 0h    |

| D[4] | CH4_PD <sup>(1)</sup> | Channel 4 Power-Down 0 = channel is on 1 = channel is power down   |         | R/W  | 0h    |

| D[3] | CH3_PD                | Channel 3 Power-Down 0 = channel is on. 1 = channel is power down. |         | R/W  | 0h    |

| D[2] | CH2_PD                | Channel 2 Power-Down 0 = channel is on 1 = channel is power down   |         | R/W  | 0h    |

| D[1] | CH1_PD                | Channel 1 Power-Down 0 = channel is on 1 = channel is power down   |         | R/W  | 0h    |

| D[0] | CH0_PD                | Channel 0 Power-Down 0 = channel is on 1 = channel is power down   |         | R/W  | 0h    |

#### NOTE:

<sup>1.</sup> The bits or registers are not included in the SGM5152H4.

# 16-Bit, 500kSPS, 4- and 8-Channel, Single Supply, SAR ADCs with Bipolar Input Ranges

## **REGISTER MAPS (continued)**

### **Device Feature Selection Control Register (Address = 03h)**

#### **Table 5. Feature Select Register Details**

| BITS   | BIT NAME | DESCRIPTION                                                                                                                                                                        | COMMENT          | TYPE | RESET |

|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------|-------|

| D[7:6] | DEV[1:0] | Device ID Bits 00 = ID for device 0 in daisy-chain mode 01 = ID for device 1 in daisy-chain mode 10 = ID for device 2 in daisy-chain mode 11 = ID for device 3 in daisy-chain mode |                  | R/W  | 0h    |

| D[5]   | 0        | Must always be set to 0                                                                                                                                                            |                  | R    | 0h    |

| D[4]   | 0        | Must always be set to 0                                                                                                                                                            |                  | R    | 0h    |

| D[3]   | 0        | Must always be set to 0                                                                                                                                                            |                  | R    | 0h    |

| D[2:0] | SDO[2:0] | SDO Data Format Bits                                                                                                                                                               | Refer to Table 6 | R/W  | 0h    |

#### **Table 6. SDO Data Format**

| SDO Format | Beginning of The Output Bit                    | Output Format                                      |                     |                                  |                   |  |  |

|------------|------------------------------------------------|----------------------------------------------------|---------------------|----------------------------------|-------------------|--|--|

| SDO[2:0]   | Stream                                         | BITS [24:9]                                        | BITS [8:5]          | BITS [4:3]                       | BITS [2:0]        |  |  |

| 000        | 16 <sup>th</sup> SCLK falling edge, no latency | Conversion result for selected channel (MSB-first) | SDO pulled low      |                                  |                   |  |  |

| 001        | 16 <sup>th</sup> SCLK falling edge, no latency | Conversion result for selected channel (MSB-first) | Channel address (1) | SDO pu                           | ılled low         |  |  |

| 010        | 16 <sup>th</sup> SCLK falling edge, no latency | Conversion result for selected channel (MSB-first) | Channel address (1) | Device<br>address <sup>(1)</sup> | SDO pulled<br>low |  |  |

| 011        | 16 <sup>th</sup> SCLK falling edge, no latency | Conversion result for selected channel (MSB-first) | Channel address (1) | Device<br>address <sup>(1)</sup> | Input range (1)   |  |  |

#### NOTE:

1. Table 7 lists the bit descriptions for these channel addresses, device addresses, and input range.

#### **Table 7. SDO Data Bit Details**

| BITS    | DESCRIPTION                                                                                                                                                                                                                                                                                                  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D[24:9] | 16 bits of conversion result for the channel represented in MSB-first format.                                                                                                                                                                                                                                |

| D[8:5]  | Four Bits of Channel Address  0000 = Channel 0  0001 = Channel 1  0010 = Channel 2  0011 = Channel 3  0100 = Channel 4 (valid only for the SGM51652H8)  0101 = Channel 5 (valid only for the SGM51652H8)  0110 = Channel 6 (valid only for the SGM51652H8)  0111 = Channel 7 (valid only for the SGM51652H8) |

| D[4:3]  | Two bits of device address (mainly useful in daisy-chain mode).                                                                                                                                                                                                                                              |

| D[2:0]  | Three LSB bits of input voltage range (refer to the Range Select Registers section).                                                                                                                                                                                                                         |

# 16-Bit, 500kSPS, 4- and 8-Channel, Single Supply, SAR ADCs with Bipolar Input Ranges

## **REGISTER MAPS (continued)**

### Range Select Registers (Addresses 05h - 0Ch)

#### Table 8. Channel n Input Range Registers Details

| BITS   | BIT NAME       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                    | COMMENT | TYPE | RESET |

|--------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|

| D[7:4] | 0              | Must always be set to 0                                                                                                                                                                                                                                                                                                                                        |         | R    | 0h    |

| D[3:0] | Range_CHn[3:0] | Input range selection bits for channel n (n = 0 to 3 for the SGM51652H4 and n = 0 to 7 for the SGM51652H8) 0000 = Input range is set to $\pm 2.5 \times V_{REF}$ 0001 = Input range is set to $\pm 1.25 \times V_{REF}$ 0010 = Input range is set to $\pm 0.625 \times V_{REF}$ 0101 = Input range is set to 0 to $\pm 0.500000000000000000000000000000000000$ |         | R/W  | 0h    |

### Command Read-Back Register (Address = 3Fh)

### Table 9. Command Read-Back Register Details

| BITS   | BIT NAME           | DESCRIPTION                             | COMMENT | TYPE | RESET |

|--------|--------------------|-----------------------------------------|---------|------|-------|

| D[7:0] | COMMAND_WORD[15:8] | Command executed in previous data frame |         | R    | 0h    |

# 16-Bit, 500kSPS, 4- and 8-Channel, Single Supply, SAR ADCs with Bipolar Input Ranges

## **REGISTER MAPS (continued)**

Input Floating Detection and Status (Address = 0Dh - 0Eh)

Table 10. INPUT\_FLOATING\_DETECTION\_EN Register Details (Address = 0Dh)

| BITS | BIT NAME   | DESCRIPTION                                                                                                               | COMMENT | TYPE | RESET |

|------|------------|---------------------------------------------------------------------------------------------------------------------------|---------|------|-------|

| D[7] | CH7_EN (1) | Channel 7 Enable 0 = Channel 7 is disabled in FLOATING_DETECTION mode 1 = Channel 7 is enabled in FLOATING_DETECTION mode |         | R/W  | 0h    |

| D[6] | CH6_EN (1) | Channel 6 Enable 0 = Channel 6 is disabled in FLOATING_DETECTION mode 1 = Channel 6 is enabled in FLOATING_DETECTION mode |         | R/W  | 0h    |

| D[5] | CH5_EN (1) | Channel 5 Enable 0 = Channel 5 is disabled in FLOATING_DETECTION mode 1 = Channel 5 is enabled in FLOATING_DETECTION mode |         | R/W  | 0h    |

| D[4] | CH4_EN (1) | Channel 4 Enable 0 = Channel 4 is disabled in FLOATING_DETECTION mode 1 = Channel 4 is enabled in FLOATING_DETECTION mode |         | R/W  | 0h    |

| D[3] | CH3_EN     | Channel 3 Enable 0 = Channel 3 is disabled in FLOATING_DETECTION mode 1 = Channel 3 is enabled in FLOATING_DETECTION mode |         | R/W  | 0h    |

| D[2] | CH2_EN     | Channel 2 Enable 0 = Channel 2 is disabled in FLOATING_DETECTION mode 1 = Channel 2 is enabled in FLOATING_DETECTION mode |         | R/W  | 0h    |

| D[1] | CH1_EN     | Channel 1 Enable 0 = Channel 1 is disabled in FLOATING_DETECTION mode 1 = Channel 1 is enabled in FLOATING_DETECTION mode |         | R/W  | 0h    |

| D[0] | CH0_EN     | Channel 0 Enable 0 = Channel 0 is disabled in FLOATING_DETECTION mode 1 = Channel 0 is enabled in FLOATING_DETECTION mode |         | R/W  | 0h    |

### NOTE:

Table 11. INPUT\_FLOATING\_DETECTION\_STATUS Register Details (Address = 0Eh)

| BITS | BIT NAME              | DESCRIPTION                                                                                             | COMMENT | TYPE | RESET |

|------|-----------------------|---------------------------------------------------------------------------------------------------------|---------|------|-------|

| D[7] | CH7_FT <sup>(1)</sup> | Channel 7 FLOATINT_STATUS 0 = Channel 7 is not in FLOATING status 1 = Channel 7 is in FLOATING status   |         | R/W  | 0h    |

| D[6] | CH6_FT <sup>(1)</sup> | Channel 6 FLOATINT_STATUS 0 = Channel 6 is not in FLOATING status 1 = Channel 6 is in FLOATING status   |         | R/W  | 0h    |

| D[5] | CH5_FT <sup>(1)</sup> | Channel 5 FLOATINT_STATUS  0 = Channel 5 is not in FLOATING status  1 = Channel 5 is in FLOATING status |         | R/W  | 0h    |

| D[4] | CH4_FT <sup>(1)</sup> | Channel 4 FLOATINT_STATUS 0 = Channel 4 is not in FLOATING status 1 = Channel 4 is in FLOATING status   |         | R/W  | 0h    |

| D[3] | CH3_FT                | Channel 3 FLOATINT_STATUS 0 = Channel 3 is not in FLOATING status 1 = Channel 3 is in FLOATING status   |         | R/W  | 0h    |

| D[2] | CH2_FT                | Channel 2 FLOATINT_STATUS 0 = Channel 2 is not in FLOATING status 1 = Channel 2 is in FLOATING status   |         | R/W  | 0h    |

| D[1] | CH1_FT                | Channel 1 FLOATINT_STATUS 0 = Channel 1 is not in FLOATING status 1 = Channel 1 is in FLOATING status   |         | R/W  | 0h    |

| D[0] | CH0_FT                | Channel 0 FLOATINT_STATUS 0 = Channel 0 is not in FLOATING status 1 = Channel 0 is in FLOATING status   |         | R/W  | 0h    |

#### NOTE:

<sup>1.</sup> The bits or registers are not included in the SGM5152H4.

<sup>1.</sup> The bits or registers are not included in the SGM5152H4.

# 16-Bit, 500kSPS, 4- and 8-Channel, Single Supply, SAR ADCs with Bipolar Input Ranges

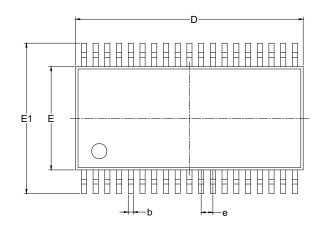

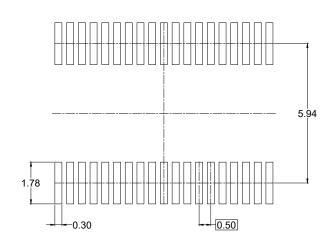

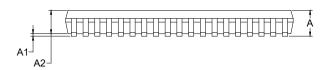

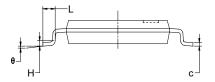

## **PACKAGE OUTLINE DIMENSIONS**

## TSSOP-38

RECOMMENDED LAND PATTERN (Unit: mm)

| Symbol | Dimensions<br>In Millimeters |       | Dimensions<br>In Inches |       |

|--------|------------------------------|-------|-------------------------|-------|

|        | MIN                          | MAX   | MIN                     | MAX   |

| Α      |                              | 1.200 |                         | 0.047 |

| A1     | 0.050                        | 0.150 | 0.002                   | 0.006 |

| A2     | 0.800                        | 1.000 | 0.031                   | 0.039 |

| b      | 0.170                        | 0.270 | 0.007                   | 0.011 |

| С      | 0.090                        | 0.200 | 0.004                   | 0.008 |

| D      | 9.600                        | 9.800 | 0.378                   | 0.386 |

| Е      | 4.300                        | 4.500 | 0.169                   | 0.177 |

| E1     | 6.250                        | 6.550 | 0.246                   | 0.258 |

| е      | 0.500 BSC                    |       | 0.020 BSC               |       |

| Н      | 0.250 TYP 0.010 TYP          |       | ) TYP                   |       |

| L      | 0.450                        | 0.750 | 0.018                   | 0.030 |

| θ      | 1°                           | 7°    | 1°                      | 7°    |

#### NOTES:

- 1. Body dimensions do not include mode flash or protrusion.

- 2. This drawing is subject to change without notice.