## I<sup>2</sup>C Controlled 13.5V/3A, 1-Cell Battery Charger with Power Path Management

### DESCRIPTION

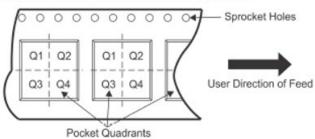

The ETA6953 is a highly-integrated 3.0-A switch-mode battery charge management and system power path management device for single cell Li-lon and Li-polymer battery. It features fast charging with high input voltage support for a wide range of smart phones, tablets and portable devices. Its low impedance power path optimizes switch-mode operation efficiency, reduces battery charging time and extends battery life during discharging phase. Its input voltage and current regulation deliver maximum charging power to battery. The solution is highly integrated with input reverse-blocking FET (RBFET, Q1), high-side switching FET (HSFET, Q2), low-side switching FET (LSFET, Q3), and battery FET (BATFET, Q4) between system and battery. It also integrates the bootstrap diode for the high-side gate drive for simplified system design. The I2C serial interface with charging and system settings makes the device a truly flexible solution.

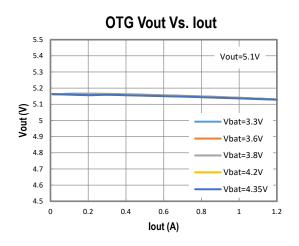

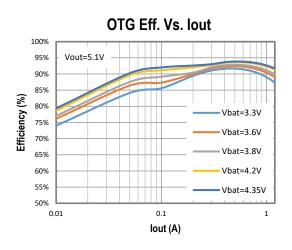

The device supports a wide range of input sources: standard USB host port, USB charging port, and USB compliant high voltage adapter. To support fast charging using high voltage adapter, the ETA6953 provides PSEL pin for USB switch control. To set the default input current limit, device takes the result from detection circuit in the system, such as USB PHY device. The device is compliant with USB 2.0 and USB 3.0 power spec with input current and voltage regulation. The device also meets USB Onthe-Go (OTG) operation power rating specification by supplying 5.15 V on VBUS with constant current limit up to 1.2-A.

The power path management regulates the system slightly above battery voltage but does not drop below 3.5 V minimum system voltage (programmable). With this feature, the system maintains operation even when the battery is completely depleted or removed. When the input current limit or voltage limit is reached, the power path management automatically reduces the charge current to zero. As the system load continues to increase, the power path discharges the battery until the system power requirement is met. This Supplement Mode prevents overloading the input source.

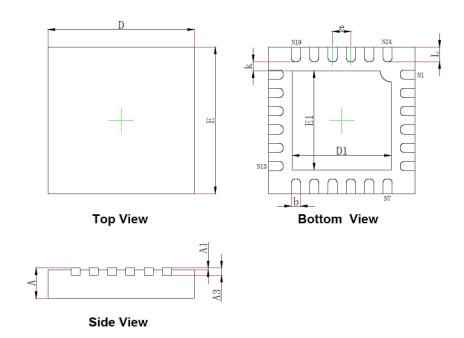

The ETA6953 is available in a QFN4x4-24L package.

### **FEATURES**

- High-Efficiency, 1.5MHz, Synchronous Switching Buck Charger

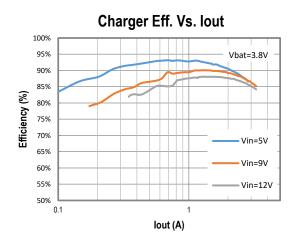

- > 90% Charge Efficiency at 2A from 5V Input

- Programmable PFM Mode for Light Load Conditions

- Supports USB On-The-Go (OTG)

- Programmable Current Limit Boost Converter with Up to 1.2A Output

- > 91% Boost Efficiency at 1A Output

- > Output Short Circuit Protection

- > Programmable PFM Mode for Light Load Conditions

- Wide Range Single Input to Support both USB Input and High Voltage Adapters

- Support 3.9V to 13.5V Input Voltage Range With 30V Absolute Maximum Input Voltage Rating

- Programmable Input Current Limit (100mA to 3.2A With 100mA Resolution) to Support USB 2.0, USB 3.0 Standards and High Voltage Adaptors (IINDPM)

- High Battery Discharge Efficiency With 27mΩ Battery Discharge MOSFET

- Narrow VDC (NVDC) Power Path Management

- BATFET Control to Support Ship Mode, Wake Up and Full System Reset

- Flexible Autonomous and I<sup>2</sup>C Mode for Optimal System Performance

- High Integration Includes All MOSFETs, Current Sensing and Loop Compensation

- 26uA Low Battery Leakage Current to Support Ship Mode

- Safety

- Battery Temperature Sensing for Charge and Boost Mode

- > Thermal Regulation and Thermal Shutdown

- Input UVLO and Overvoltage Protection

### **APPLICATIONS**

- Tablet PC, Smart Phone, Internet Devices

- Portable Audio Speaker

- Handheld Computers, PDA, POS

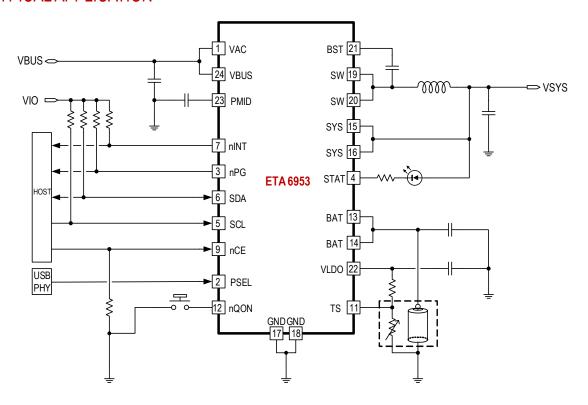

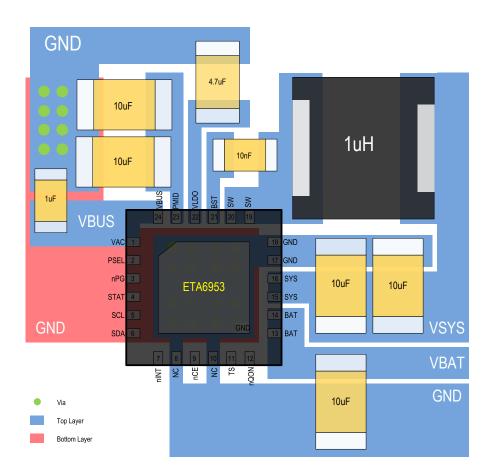

### TYPICAL APPLICATION

ORDERING INFORMATION PART No. PACKAGE TOP MARK Pcs/Reel

ETA6953Q4Y QFN4x4-24 ETA6953

YWW2L 5000

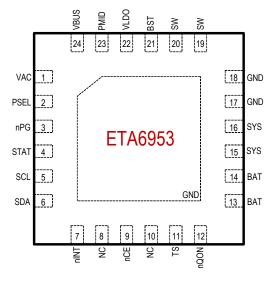

## PIN CONFIGURATION

QFN4 x 4 - 24

## ABSOLUTE MAXIMUM RATINGS

(Note: Exceeding these limits may damage the device. Exposure to absolute maximum rating conditions for long periods may affect device reliability.)

| VAC, VBUS, PMID to GND Voltage                 | 2V to 30V          |

|------------------------------------------------|--------------------|

| SW to GND Voltage                              | 0.3V to 20V        |

| nPG, STAT to GND Voltage                       | 0.3V to 12V        |

| SYS, BAT to GND Voltage                        | –0.3V to 6V        |

| BST to SW Voltage                              | –0.3V to 6V        |

| All Other Pin to GND Voltage                   | –0.3V to 6V        |

| SW, VBUS, BAT, SYS to PGND current             | Internally limited |

| Operating Temperature Range                    | 40°C to 85°C       |

| Storage Temperature Range                      | 55°C to 150°C      |

| Thermal Resistance $\theta_{JA}$ $\theta_{JC}$ |                    |

| QFN4x4–24pin3510                               | °C/W               |

| Lead Temperature (Soldering, 10sec)            | 260°C              |

## **ELECTRICAL CHARACTERISTICS**

(Vbat = 3.6V, unless otherwise specified. Typical values are at  $T_A$  = 25°C.)

| PARAMETER                                                           | CONDITIONS                                                                                                                         | MIN  | TYP  | MAX  | UNITS |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| QUIESCENT CURRENTS                                                  |                                                                                                                                    |      |      |      |       |

| Battery discharge current (BAT, SW, SYS) in buck mode               | V <sub>BAT</sub> = 4.5V, V <sub>VBUS</sub> < V <sub>BUS-UVLOZ</sub> ,<br>leakage between BAT and VBUS, T <sub>J</sub> < 85°C       |      |      | 5    | μА    |

| Battery discharge current (BAT) in buck mode                        | $V_{BAT}$ = 4.5V, HIZ Mode and BATFET_DIS = 1 or No VBUS, I <sup>2</sup> C disabled, BATFET Disabled. $T_{J}$ < 85°C               |      | 26   | 50   | μA    |

| Battery discharge current (BAT, SW, SYS)                            | V <sub>BAT</sub> = 4.5V, HIZ Mode and OVPFET_DIS = 1 or No VBUS, I2C Disabled, BATFET Enabled. T <sub>J</sub> < 85°C               |      | 100  | 180  | μΑ    |

| Input supply current (VBUS) in buck mode                            | $V_{VBUS}$ > $V_{BUS\_UVLO}$ , $V_{BUS}$ > $V_{BAT}$ , converter switching, $V_{BAT}$ = 3.8V, $I_{SYS}$ = 0A                       |      | 5    |      | mA    |

| Battery Discharge Current in boost mode                             | V <sub>BAT</sub> = 4.2V, boost mode, I <sub>VBUS</sub> = 0A, converter switching                                                   |      | 2    |      | mA    |

| VBUS, VAC AND BAT PIN POWER-UP                                      |                                                                                                                                    |      |      |      |       |

| VBUS operating range                                                | V <sub>VBUS</sub> rising                                                                                                           | 3.9  |      | 13.5 | V     |

| VBUS for active I <sup>2</sup> C, no battery Sense VBUS pin voltage | V <sub>VBUS</sub> rising                                                                                                           |      | 3.3  | 3.6  | V     |

| I <sup>2</sup> C active hysteresis                                  | V <sub>VBUS</sub> falling from above V <sub>VBUS_UVLO</sub>                                                                        |      | 300  |      | mV    |

| One of the conditions to turn on VLDO                               | V <sub>VBUS</sub> rising                                                                                                           |      | 3.65 | 3.9  | V     |

| One of the conditions to turn on VLDO                               | V <sub>VBUS</sub> falling                                                                                                          |      | 500  |      | mV    |

| Sleep mode falling threshold                                        | (V <sub>VBUS</sub> -V <sub>BAT</sub> ), V <sub>BUSMIN_FALL</sub> ≤ V <sub>BAT</sub> ≤ V <sub>REG</sub> , V <sub>VBUS</sub> falling |      | 60   | 110  | mV    |

| Sleep mode rising threshold                                         | (VVAC–VVBAT ), VBUSMIN_FALL ≤ VBAT ≤ VREG, VAC rising                                                                              | 110  | 220  | 330  | mV    |

| VBUS 6.5V Overvoltage rising threshold                              | V <sub>VBUS</sub> rising, OVP<1:0> = '01'                                                                                          | 6    | 6.5  | 7    | V     |

| VBUS 11V Overvoltage rising threshold                               | V <sub>VBUS</sub> rising, OVP<1:0> = '10'                                                                                          | 10   | 11   | 12   | V     |

| VBUS 14V Overvoltage rising threshold                               | V <sub>VBUS</sub> rising, OVP<1:0> = '11'                                                                                          | 13   | 14   | 15   | V     |

| VBUS 6.5V Overvoltage hysteresis                                    | V <sub>VBUS</sub> falling, OVP<1:0> = '01'                                                                                         |      | 220  |      | mV    |

| VAC 11V Overvoltage hysteresis                                      | V <sub>VBUS</sub> falling, OVP<1:0> = '10'                                                                                         |      | 400  |      | mV    |

| VAC 14V Overvoltage hysteresis                                      | V <sub>VBUS</sub> falling, OVP<1:0> = '11'                                                                                         |      | 500  |      | mV    |

| BAT for active I <sup>2</sup> C, no adapter                         | VBAT rising                                                                                                                        | 2.5  | 2.7  |      | V     |

| Battery Depletion Threshold                                         | VBAT falling                                                                                                                       | 2.2  | 2.4  | 2.6  | V     |

| Battery Depletion Threshold                                         | VBAT rising                                                                                                                        | 2.35 | 2.58 | 2.8  | V     |

| Battery Depletion rising hysteresis                                 | VBAT rising                                                                                                                        |      | 180  |      | mV    |

| Bad adapter detection falling threshold                             | VBUS falling                                                                                                                       | 3.7  | 3.9  | 4.1  | V     |

| Bad adapter detection hysteresis                                    |                                                                                                                                    |      | 80   |      | mV    |

| Bad adapter detection current source                                | Sink current from VBUS to GND                                                                                                      |      | 30   |      | mA    |

| PARAMETER                                                                | CONDITIONS                                                                                      | MIN   | TYP                 | MAX   | UNITS |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|-------|---------------------|-------|-------|

| POWER-PATH                                                               |                                                                                                 |       |                     |       |       |

| System regulation voltage                                                | V <sub>BAT</sub> < SYS_MIN[2:0] = 101,<br>BATFET Disabled (REG07[5] = 1)                        |       | 3.68                |       | V     |

| System Regulation Voltage                                                | $I_{SYS} = 0A$ , $V_{BAT} > V_{SYS\_MIN}$ , $V_{BAT} = 4.400V$ , BATFET disabled (REG07[5] = 1) |       | V <sub>BAT</sub> +7 |       |       |

| Maximum DC system voltage output                                         | $I_{SYS}$ = 0A, Q4 off, $V_{BAT} \le 4.400V$ , $V_{BAT} > V_{SYSMIN}$ = 3.5V                    |       | 4.47                |       | V     |

| Top reverse blocking MOSFET on-<br>resistance between VBUS and PMID - Q1 | -40°C≤ TA ≤ 125°C                                                                               | 20    | 40                  | 60    | mΩ    |

| Top switching MOSFET on-<br>resistance between PMID and SW - Q2          | V <sub>VLDO</sub> = 5 V , -40°C≤ T <sub>A</sub> ≤ 125°C                                         | 35    | 70                  | 105   | mΩ    |

| Bottom switching MOSFET on-resistance between SW and GND - Q3            | V <sub>VLDO</sub> = 5 V , -40°C≤ T <sub>A</sub> ≤ 125°C                                         | 21    | 43                  | 65    | mΩ    |

| SYS-BAT MOSFET on-resistance – Q4                                        | QFN package, Measured from BAT to SYS, V <sub>BAT</sub> = 4.2V, T <sub>J</sub> = -40 - 125°C    | 13    | 27                  | 40    | mΩ    |

| BATFET forward voltage in supplement mode                                |                                                                                                 |       | 30                  |       | mV    |

| BATTERY CHARGER                                                          |                                                                                                 |       |                     |       |       |

| Change voltage program range                                             |                                                                                                 | 3.856 |                     | 4.624 | V     |

| Charge voltage step                                                      |                                                                                                 |       | 32                  |       | mV    |

| Charge voltage setting                                                   | VREG (REG04[7:3]) = 4.208 V<br>(01011), V, -40 ≤ TJ ≤ 85°C                                      | 4.187 | 4.208               | 4.229 | V     |

| Charge voltage setting accuracy                                          | VBAT = 4.208 V or VBAT = 4.352 V,<br>-40 ≤ TJ ≤ 85°C                                            | -0.5  |                     | +0.5  | %     |

| Charge current regulation range                                          |                                                                                                 | 0     |                     | 3000  | mA    |

| Charge current regulation step                                           |                                                                                                 |       | 60                  |       | mA    |

| Charge current regulation setting                                        | $I_{CHG}$ = 1980mA, $V_{VBAT}$ = 3.1V or $V_{VBAT}$ = 3.8V                                      |       | 1980                |       | mA    |

| Charge current regulation accuracy                                       | $I_{CHG}$ = 1980mA, $V_{VBAT}$ = 3.1V or $V_{VBAT}$ = 3.8V                                      | -10   |                     | +10   | %     |

| Battery LOWV falling threshold                                           | I <sub>CHG</sub> = 1980mA                                                                       | 2.6   | 2.8                 | 3     | V     |

| Battery LOWV rising threshold                                            | Pre-charge to fast charge                                                                       | 2.9   | 3.1                 | 3.3   | V     |

| Precharge current regulation                                             | IPRECHG[3:0] = '0010' = 180mA                                                                   | 144   | 180                 | 216   | mA    |

| Termination current regulation                                           | I <sub>CHG</sub> >780 mA, ITERM[3:0] = '0010'<br>V <sub>VBAT</sub> = 4.208V                     | 144   | 180                 | 216   | mA    |

| Battery short voltage                                                    | V <sub>VBAT</sub> falling                                                                       | 1.8   | 2                   | 2.2   | V     |

| Battery short voltage                                                    | V <sub>VBAT</sub> rising                                                                        | 2.05  | 2.25                | 2.45  | ٧     |

| Battery short current                                                    | V <sub>VBAT</sub> =1V                                                                           |       | 145                 |       | mA    |

| Recharge Threshold below V <sub>BAT_REG</sub>                            | V <sub>BAT</sub> falling, REG04[0] = 0                                                          | 70    | 120                 | 170   | mV    |

| Recharge Threshold below V <sub>BAT_REG</sub>                            | V <sub>BAT</sub> falling, REG04[0] = 1                                                          | 190   | 240                 | 290   | mV    |

| INPUT VOLTAGE AND CURRENT REGUL                                          |                                                                                                 | 1     | 1                   | 1     |       |

| Input voltage regulation limit                                           | VINDPM[3:0] = 0110 = 4.5 V                                                                      | 4.32  | 4.5                 | 4.68  | V     |

| PARAMETER                                            | CONDITIONS                                                      | MIN  | TYP  | MAX  | UNITS |

|------------------------------------------------------|-----------------------------------------------------------------|------|------|------|-------|

| Input voltage regulation accuracy                    |                                                                 | -4   |      | 4    | %     |

| Input voltage regulation limit tracking              | VINDPM[3:0] = 3.9V, VDPM_VBAT_TRACK =                           | 4.13 | 4.3  | 4.47 | V     |

| VBAT                                                 | 300mV, VBAT = 4.0V                                              | 4.13 | 4.3  | 4.41 | V     |

|                                                      | V <sub>VBUS</sub> = 5V, current pulled from SW,                 |      |      |      |       |

| USB input current regulation limit                   | IINDPM [4:0] = 10111 = 2.4 A,                                   | 2.16 | 2.4  | 2.64 | A     |

|                                                      | -40 ≤ T <sub>J</sub> ≤ 85°C                                     |      |      |      |       |

| Input current limit during system start-up           |                                                                 |      | 200  |      | mA    |

| sequence                                             |                                                                 |      | 200  |      |       |

| BAT PIN OVERVOLTAGE PROTECTION                       |                                                                 | 1    | 1    | 1    |       |

| Battery overvoltage threshold                        | V <sub>BAT</sub> rising, as percentage of V <sub>BAT_REG</sub>  |      | 108  |      | %     |

| Battery overvoltage threshold Hysteresis             | V <sub>BAT</sub> falling, as percentage of V <sub>BAT_REG</sub> |      | 103  |      | %     |

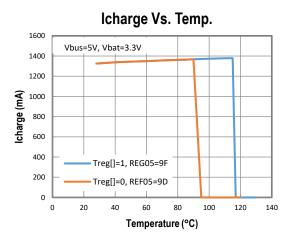

| THERMAL REGULATION AND THERMAL                       | SHUTDOWN                                                        |      |      |      |       |

| Junction Temperature Regulation                      | Temperature Increasing, TREG = 1                                |      | 110  |      | °C    |

| Threshold                                            | remperature increasing, rives                                   |      | 110  |      |       |

| Junction Temperature Regulation                      | Temperature Increasing, TREG = 0                                |      | 90   |      | °C    |

| Threshold                                            | Temperature increasing, TNEO = 0                                |      | 30   |      |       |

| Thermal Shutdown Rising Temperature                  |                                                                 |      | 160  |      | °C    |

| Thermal Shutdown Hysteresis                          |                                                                 |      | 30   |      | °C    |

| JEITA Thermistor Comparator (BUCK MC                 | DDE)                                                            |      |      |      |       |

| T1 (0°C) threshold, Charge suspended T1              | Charger suspends charge. As Percentage to                       |      | 73.3 | 0    |       |

| below this temperature.                              | V <sub>LDO</sub>                                                |      | 73.3 |      | %     |

| Falling                                              | As Percentage to V <sub>LDO</sub>                               |      | 71.5 |      | %     |

| T2 (10°C) threshold, Charge back to                  | As Demontors to V                                               |      | 68   |      | %     |

| I <sub>CHG</sub> /2 and 4.2 V below this temperature | As Percentage to V <sub>LDO</sub>                               |      | 00   |      | 70    |

| Falling                                              | As Percentage to V <sub>LDO</sub>                               |      | 66.8 |      | %     |

| T3 (45°C) threshold, charge back to I <sub>CHG</sub> | Charger suspends charge. As Percentage to                       |      | 44.7 |      | %     |

| and 4.05V above this temperature.                    | V <sub>LDO</sub>                                                |      | 44.7 |      | 70    |

| Falling                                              | As Percentage to V <sub>LDO</sub>                               |      | 45.7 |      |       |

| T5 (60°C) threshold, charge suspended                | As Demontors to V                                               |      | 24.2 |      | %     |

| above this temperature.                              | As Percentage to V <sub>LDO</sub>                               |      | 34.2 |      | 70    |

| Falling                                              | As Percentage to V <sub>LDO</sub>                               |      | 35.3 |      | %     |

| COLD OR HOT THERMISTER COMPARA                       | TOR (BOOST MODE)                                                |      |      |      | •     |

| Cold Temperature Threshold, TS pin                   | As Percentage to V <sub>LDO</sub> (Approx20°C w/                | 70   | 00.0 | 00   | 0/    |

| Voltage Rising Threshold                             | 103AT), TJ = -20°C - 125°C                                      | 78   | 80.0 | 82   | %     |

| Falling                                              | TJ = -20°C - 125°C                                              | 77   | 79.0 | 81   | %     |

| Hot Temperature Threshold, TS pin                    | As Percentage to V <sub>LDO</sub> (Approx. 60°C w/              | 00.0 | 24.0 | 22.0 | 0/    |

| Voltage falling Threshold                            | 103AT), TJ = –20°C - 125°C                                      | 29.2 | 31.2 | 33.2 | %     |

| Rising                                               | TJ = -20°C - 125°C                                              | 32.4 | 34.4 | 36.4 | %     |

| CHARGE OVERCURRENT COMPARATOR                        | R (CYCLE-BY-CYCLE)                                              |      | 1    |      |       |

| PARAMETER                                 | CONDITIONS                                                               | MIN | TYP  | MAX | UNITS |

|-------------------------------------------|--------------------------------------------------------------------------|-----|------|-----|-------|

| HSFET cycle-by-cycle over-current         |                                                                          | 4.8 | 5.8  | 7.5 | А     |

| threshold                                 |                                                                          | 4.0 | 5.0  | 7.5 | A     |

| System over load threshold                |                                                                          | 4.7 | 5.2  | 5.7 | Α     |

| CHARGE UNDER-CURRENT COMPARAT             | OR (CYCLE-BY-CYCLE)                                                      |     |      |     |       |

| LSFET under-current falling threshold     | From sync mode to non-sync mode                                          |     | 250  |     | mA    |

| PWM                                       |                                                                          |     |      |     |       |

| PWM switching frequency                   | Oscillator frequency                                                     |     | 1500 |     | kHz   |

| Maximum PWM duty cycle                    |                                                                          |     | 97   |     | %     |

| BOOST MODE OPERATION                      |                                                                          |     |      |     |       |

| Boost mode regulation voltage             | V <sub>VBAT</sub> = 3.8 V, I <sub>(PMID)</sub> = 0 A, BOOSTV[1:0] = '10' | 5   | 5.15 | 5.3 | V     |

| Boost mode regulation voltage accuracy    | V <sub>VBAT</sub> = 3.8 V, I <sub>(PMID)</sub> = 0 A, BOOSTV[1:0] = '10' | -3  |      | 3   | %     |

|                                           | V <sub>VBAT</sub> falling, MIN_VBAT_SEL = 0                              | 2.6 | 2.8  | 3.0 | V     |

| Dellami voltana avillina kasat varida     | V <sub>VBAT</sub> rising, MIN_VBAT_SEL =0                                | 2.8 | 3    | 3.2 | V     |

| Battery voltage exiting boost mode        | V <sub>VBAT</sub> falling, MIN_VBAT_SEL = 1                              | 2.3 | 2.5  | 2.7 | V     |

|                                           | V <sub>VBAT</sub> rising, MIN_VBAT_SEL = 1                               | 2.6 | 2.8  | 3.0 | V     |

| OTG mode output current                   | BOOST_LIM = 1                                                            | 1.2 | 1.4  |     | Α     |

| ·                                         | BOOST_LIM = 0                                                            | 0.5 | 0.7  |     | Α     |

| OTG overvoltage threshold                 | Rising threshold                                                         | 5.6 | 6    | 6.4 | V     |

| HSFET under current falling threshold     |                                                                          |     | 100  |     | mA    |

| Hiccup Retrying timer                     |                                                                          |     | 7    |     | ms    |

| Hiccup Off timer                          |                                                                          |     | 28   |     | ms    |

|                                           | After the last retry, part clear OTG_CONFIG                              |     | _    |     | _     |

| Maximum retry allowed                     | bit to disable Boost                                                     |     | 7    |     | Time  |

| VLDO REGULATION                           |                                                                          |     |      |     |       |

| LDO output voltage                        | $V_{VBUS} = 9V$ , $I_{LDO} = 40$ mA                                      |     | 5    |     | V     |

| LDO output current limit                  | V <sub>VBUS</sub> = 9V, V <sub>LDO</sub> = 4V                            |     | 80   |     | mA    |

| LOGIC I/O PIN CHARACTERISTICS (nCE        | , PSEL, SCL, SDA)                                                        |     |      |     |       |

| Input low threshold                       |                                                                          |     |      | 0.4 | V     |

| Input high threshold                      |                                                                          | 1.3 |      |     | V     |

| High-level leakage current                | Pull up rail 1.8 V                                                       |     |      | 1   | μA    |

| LOGIC I/O PIN CHARACTERISTICS (nPG        | · ·                                                                      |     |      |     |       |

| Low-level output voltage                  |                                                                          |     |      | 0.4 | V     |

| VBUS/BAT POWER UP                         |                                                                          |     | 1    |     |       |

| Bad adapter detection duration            |                                                                          |     | 30.0 |     | ms    |

| BATTERY CHARGER                           |                                                                          |     | 1    |     |       |

| Deglitch time for charge Termination      |                                                                          |     | 7    |     | S     |

| Deglitch time for recharge                |                                                                          |     | 32   |     | ms    |

| System over-current deglitch time to turn |                                                                          |     |      |     |       |

| off Q4                                    |                                                                          |     | 1    |     | ms    |

6

| PARAMETER                                | CONDITIONS                            | MIN | TYP  | MAX | UNITS |

|------------------------------------------|---------------------------------------|-----|------|-----|-------|

| Battery over-voltage deglitch time to    |                                       |     | 10   |     |       |

| disable charge                           |                                       |     | 10   |     | μs    |

| Typical Charge Safety Timer Range        | CHG_TIMER = 1                         |     | 10   |     | Hr    |

| Typical Top-Off Timer Range              | TOP_OFF_TIMER[1:0] = 10 (30 min)      |     | 30   |     | min   |

| nQON TIMING                              |                                       |     |      |     |       |

| nQON low time to turn on BATFET and      | -10°C ≤ T <sub>1</sub> ≤ 60°C         |     | 1.15 |     |       |

| exit ship mode                           | -10°C \( \) 1 \( \) \( \) \( \) \( \) |     | 1.15 |     | S     |

| nQON low time to reset BATFET            | -10°C ≤ T <sub>J</sub> ≤ 60°C         |     | 10   |     | S     |

| BATFET off time during full system reset | -10°C ≤ T <sub>J</sub> ≤ 60°C         |     | 320  |     | ms    |

| Enter ship mode delay                    | -10 °C ≤ T <sub>J</sub> ≤ 60°C        |     | 12   |     | S     |

| DIGITAL CLOCK AND WATCHDOG TIME          | R                                     | 1   | 1    |     |       |

| REG05[4]=01                              |                                       |     | 40   |     | S     |

## PIN DESCRIPTION

| PIN NAME                                                                                                                                                       | PIN# | DESCRIPTION                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VAC                                                                                                                                                            | 1    | Charger input voltage sense. This pin must be connected to VBUS pin.                                                                                                                                                                                                                                                                                |

| VBUS                                                                                                                                                           | 24   | Charger input voltage. Bypass it with a 10-µF ceramic capacitor from VBUS to PGND. The capacitor should be close to the VBUS pin.                                                                                                                                                                                                                   |

| PSEL                                                                                                                                                           | 2    | Power source selection input. Set 500 mA input current limit by pulling this pin high and set 2.4A input current limit by pulling this pin low. Once the device gets into host mode, the host can program different input current limits to IINDPM register.                                                                                        |

| nPG                                                                                                                                                            | 3    | Open drain active low power good indicator. Connect to the pull up rail through 10-kΩ resistor. LOW indicates a good input source if the input voltage is between V <sub>BUSUVLO</sub> and V <sub>BUS_OV</sub> , above SLEEP mode threshold, and current limit is above 30 mA.                                                                      |

| STAT                                                                                                                                                           | 4    | Open-drain charge status output. Connect the STAT pin to a logic rail via 10-kΩ resistor. The STAT pin indicates charger status. Connect a current limit resistor and a LED from a rail to this pin. Charge in progress: LOW  Charge complete or charger in SLEEP mode: HIGH  Charge suspend (fault response)or No bat: 1-Hz, 50% duty cycle Pulses |

| SCL                                                                                                                                                            | 5    | I <sup>2</sup> C interface clock. Connect a 10-k $\Omega$ pull up resistor to the logic rail.                                                                                                                                                                                                                                                       |

| SDA                                                                                                                                                            | 6    | I <sup>2</sup> C interface data. Connect a 10-kΩ pull up resistor to the logic rail.                                                                                                                                                                                                                                                                |

| nINT                                                                                                                                                           | 7    | Open-drain interrupt Output. Connect the INT to a logic rail through 10-kΩ resistor. The INT pin sends an active low, 256-μs pulse to host to report charger device status and fault.                                                                                                                                                               |

| NC                                                                                                                                                             | 8    | No Connect. Keep the pin float                                                                                                                                                                                                                                                                                                                      |

| nCE                                                                                                                                                            | 9    | Charge disable control pin. nCE=0, charge is enabled. nCE=1, charge is disabled.                                                                                                                                                                                                                                                                    |

| NC                                                                                                                                                             | 10   | No Connect. Keep the pin float                                                                                                                                                                                                                                                                                                                      |

| TS Temperature qualification voltage input to support JEITA profile. Connect a coefficient thermistor. Program temperature window with a resistor divider from |      |                                                                                                                                                                                                                                                                                                                                                     |

| PIN NAME | PIN#       | DESCRIPTION                                                                                        |

|----------|------------|----------------------------------------------------------------------------------------------------|

|          |            | Charge suspends when either TS pin is out of range. When TS pin is not used, connect a 10-kΩ       |

|          |            | resistor from VLDO to TS and connect a 10-kΩ resistor from TS to GND. It is recommended to use     |

|          |            | a 103AT-2 thermistor.                                                                              |

|          |            | BATFET enable/reset control input. When BATFET is in ship mode, a logic low of tshipmode (typical  |

|          |            | 1.15s) duration turns on BATFET to exit shipping mode. When VBUS is not plugged-in, a logic low    |

| nQON     | 12         | of tqon_rst (minimum 8s) duration resets SYS (system power) by turning BATFET off for tbatfet_rst  |

|          |            | (minimum 250 ms) and then re-enable BATFET to provide full system power reset. The pin contains    |

|          |            | an internal pull-up to maintain default high logic.                                                |

| BAT      | 13, 14     | Positive battery terminal. The internal BATFET and current sensing is connected between SYS and    |

| טאו      | 10, 14     | BAT. Connect a 10 µF close to the BAT pin.                                                         |

| SYS      | 15, 16     | Converter output connection point. The internal current sensing network is connected between SYS   |

| 010      | 10, 10     | and BAT. Connect a 20 μF close to the SYS pin.                                                     |

| GND      | 17, 18     | Power Ground                                                                                       |

| SW       | 19, 20     | Switching node output. Connected to output inductor. Connect the 10nF bootstrap capacitor from     |

| OVV      | 13, 20     | SW to BTST                                                                                         |

| BST      | 21         | Bootstrap capacitor connection for the high-side FET gate driver. Connect a 10nF ceramic capacitor |

| DOT      | <b>4</b> 1 | from BST pin to SW pin.                                                                            |

| VLDO     | 22         | LDO Output Voltage. Bypass the pin with 4.7µF (10V rating) capacitor from VLDO to GND. The         |

| VLDO     |            | capacitor should be closed to the pin                                                              |

| PMID     | 23         | Connection point between reverse blocking FET and high-side switching FET. Bypass it with a        |

| I WIID   |            | minimum of 10µF capacitor from PMID to PGND. This capacitor should be close to the PMID pin.       |

|          |            | Thermal pad and ground reference. This pad is ground reference for the device and it is also the   |

| EP       | EP         | thermal pad used to conduct heat from the device. This pad should be tied externally to a ground   |

|          |            | plane through PCB vias under the pad.                                                              |

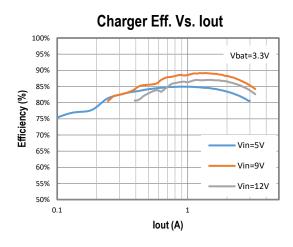

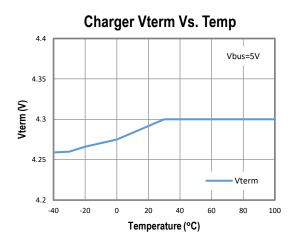

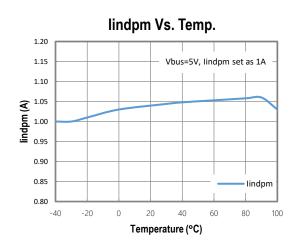

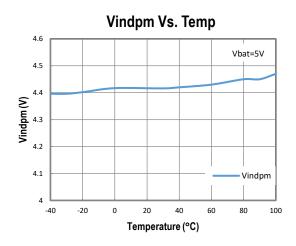

## TYPICAL PERFORMANCE CHARACTERISTICS

(Typical values are at  $T_A = 25$ °C unless otherwise specified.)

## TYPICAL PERFORMANCE CHARACTERISTICS cont'

(Typical values are at T<sub>A</sub> = 25°C unless otherwise specified.)

### **FUNCTION DESCRIPTION**

The ETA6953 device is a highly integrated 3.0-A switch-mode battery charger for single cell Li-lon and Li-polymer battery. It includes the input reverse-blocking FET (RBFET, Q1), high-side switching FET (HSFET, Q2), low-side switching FET (LSFET, Q3), and battery FET (BATFET, Q4), and bootstrap diode for the high-side gate drive

#### POWER UP FROM BATTERY WITHOUT INPUT SOURCE

When a battery is applied without other input, the device checks the battery voltage to turn on BATFET but not VLDO to minimize the supply current, especially for NTC resistor network. All supply will be directly from battery. VLDO is disabled until BOOST is enabled. Anyway, in order to optimize the discharge current from battery at light load, BATFET gate charge pump operates with lower frequency.

#### POWER UP WITH INPUT SOURCE

When an input source is plugged in, the device checks the input source voltage to turn on REGN LDO and all the bias circuits. It detects and sets the input current limit before the buck converter is started. The power up sequence from input source is as listed:

- 1. Power up VLDO

- 2. Poor Source Qualification

- 3. Input Source Type Detection based on PSEL to set default input Current Limit (IINDPM) register or input source type

- 4. Input Voltage Limit Threshold Setting (VINDPM threshold)

- 5. Converter Power-up

#### VLDO POWER UP

VLDO is enabled when the below conditions are met:

- 1. VAC is above 3.65V

- 2. VAC is above VBAT + VSLEEP (200mV)in Buck mode or VAC below VBAT + VSLEEP in Boost mode

Right after two above conditions are valid, VLDO is powered up right away

#### POWER SOURCE QUALIFICATION

After VLDO powers up, the device checks the current capability of the input source. The input source has to meet the following requirements in order to start the buck converter.

- 1. 200mS delay after VLDO enable

- 2. VAC voltage below the VAC\_OVP threshold

- 3. VAC voltage above 3.8V when pulling down 30mA at VAC

If the device fails the poor source detection in 30ms, it repeats poor source qualification every 2 seconds. Once the input source passes all the conditions above, the status register bit VBUS\_GD is set high and the nINT pin is pulsed to signal to the host.

#### INPUT SOURCE TYPE DETECTION

After the VBUS\_GD bit is set, the device will run input source detection through the PSEL pin. The ETA6953 sets input current limit through PSEL pin. And after input type detection is completed, Input Current limit register is changed to set current limit; PG\_STAT bit and VBUS\_STAT bits are updated.

#### PSEL PIN SET INPUT CURRENT LIMIT

The ETA6953 has a PSEL pin for input current limit setting. When the device works in default mode, the input current limit will be either 0.5A (PSEL High) or 2.4A (PSEL Low). When device operates in host mode, the input current limit will follow IINDPM register setting. But if it works in the host mode, then the host write IINDET\_EN bit to 1, it will force current limit to follow PSEL pin and then updates IINDPM register. After that, the IINDET\_EN bit is auto clear to 0, the IINDPM register will hold the PSEL current limit setting either 0.5A or 2.4A.

#### **BUCK POWER UP**

After the input current is set, the device starts Buck converter and allow HSFET and LSFET switching. The ETA6953 provide soft-start time, VSYS short protection to avoid overshoot current. When switching is over the soft-start time, the BATFET starts turning on then allows charging progress.

The device provides soft-start when system rail is ramped up. When the system rail is below 2.2 V, the input current limit is set to the lower of 200 mA or IINDPM register setting. After the system rises above 2.2 V, the device limits input current to the value of IINDPM register. As a battery charger, the device deploys a highly efficient 1.5 MHz step-down switching regulator. The fixed frequency oscillator keeps tight control of the switching frequency under all conditions of input voltage, battery voltage, charge current and temperature, simplifying output filter design.

In order to improve light-load efficiency, the device switches to PFM control at light load when battery is below minimum system voltage setting or charging is disabled. During the PFM operation, the switching duty cycle is set by the voltage ratio of SYS and VBUS. The PFM\_DIS bit can be used to prevent PFM operation in either buck or boost configuration.

#### **BOOST POWER UP**

ETA6953 provide boost converter up to 1.2A output current. The boost is enabled when the below conditions are valid:

- 1. VBAT above the battery voltage exiting boost mode threshold

- 2. VBUS is less than VBAT+VSLEEP (200mV)

- 3. OTG\_CONFIG bit=1

- 4. TS pin is within acceptable range (VBHOT<VTS<VBCOLD)

During boost mode, the status register VBUS\_STAT bits is set to 111, the VBUS output is 5.15 V by default and 1.5MHz Frequency. The output current can reach up to 1.2 A, selected through I2C (BOOST\_LIM bit). The boost output is maintained when BAT is above VOTG\_BAT threshold. When OTG is enabled, the device starts up with PFM and later transits to PWM to minimize the overshoot. The PFM\_DIS bit can be used to prevent PFM operation in either buck or boost configuration.

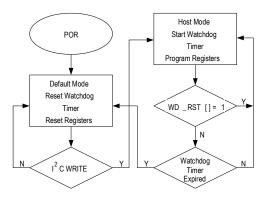

#### HOST MODE AND DEFAULT MODE

The ETA6953 is a host controlled charger, but it can operate in default mode without host management. In default mode, the device can be used as an autonomous charger with no host or while host is in sleep mode. When the charger is in default mode, WATCHDOG\_FAULT bit is Logic High. When the charger is in host mode, WATCHDOG\_FAULT bit is Logic Low.

After power-on-reset, the device starts in default mode with watchdog timer expired, or default mode. All the registers are in the default settings. During default mode, any change on PSEL pin will make real time IINDPM register changes.

In default mode, the device keeps charging the battery with default 10-hour fast charging safety timer. At the end of the 10-hour, the

charging is stopped and the buck converter continues to operate to supply system load.

Writing a '1' to the WD\_RST bit transitions the charger from default mode to host mode. All the device parameters can be programmed by the host. To keep the device in host mode, the host has to reset the watchdog timer by writing '1' to WD\_RST bit before the watchdog timer expires (WATCHDOG\_FAULT bit is set), or disable watchdog timer by setting WATCHDOG bits = 00.

When the watchdog timer expires (WATCHDOG\_FAULT bit = 1), the device returns to default mode and all registers are reset to default values except IINDPM, VINDPM, BATFET\_RST\_EN, BATFET\_DLY, and BATFET\_DIS bits.

Figure 1: Watchdog Timer Flow Chart

### **AUTONOMOUS BATTERY CHARGER**

The device charges 1-cell Li-lon battery with up to 3.0-A charge current for high capacity tablet battery. The 27mΩ BATFET improves charging efficiency and minimize the voltage drop during discharging.

With battery charging is enabled (CHG\_CONFIG bit = 1 and nCE pin is LOW), the device autonomously completes a charging cycle without host involvement. The host can always control the charging operations and optimize the charging parameters by writing to the corresponding registers through I<sup>2</sup>C.

A new charge cycle starts when the following conditions are valid:

- Converter starts

- Battery charging is enabled (CHG\_CONFIG bit = 1 and ICHG register is not 0 mA and CE is low)

- No thermistor fault on TS

- No safety timer fault

- BATFET is not forced to turn off (BATFET\_DIS bit = 0)

| Table 11 Charging Farameter Berault Collin | 19       |

|--------------------------------------------|----------|

| <b>Default Mode</b>                        | ETA6953  |

| Charging Voltage                           | 4.208V   |

| Charging Current                           | 2.048A   |

| Pre-charge Current                         | 180mA    |

| Termination Current                        | 180mA    |

| Temperature Profile                        | JEITA    |

| Safety Timer                               | 10 hours |

Table 1: Charging Parameter Default Setting

The charger device automatically terminates the charging cycle when the charging current is below termination threshold, charge voltage is above recharge threshold, and device not is in DPM mode or thermal regulation.

When a full battery voltage is discharged below recharge threshold (selectable through VRECHG bit), the device automatically starts a new charging cycle. After the charge is done, toggle nCE pin or CHG\_CONFIG bit can initiate a new charging cycle.

The STAT output indicates the charging status: charging (LOW), charging complete or charge disable (HIGH) or charging fault (Blinking). The STAT output can be disabled by setting EN\_ICHG\_MON bits = 11. In addition, the status register (CHRG\_STAT) indicates the different charging phases: 00-charging disable, 01-precharge, 10-fast charge (constant current) and constant voltage mode, 11-charging done. Once a charging cycle is completed, an INT is asserted to notify the host.

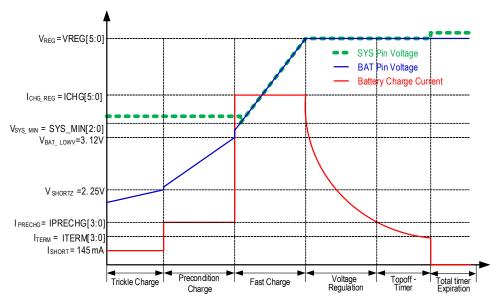

#### **BATTERY CHARGER PROFILE**

The device charges the battery in five phases: battery short, preconditioning, constant current, constant voltage and top-off trickle charging (optional). At the beginning of a charging cycle, the device checks the battery voltage and regulates current and voltage accordingly.

If the charger device is in DPM regulation or thermal regulation during charging, the actual charging current will be less than the programmed value. in this case, termination is temporarily disabled and the charging safety timer is counted at half the clock rate.

Figure 2: Battery Charger Profile

#### CHARGE TERMINATION CONFIGURATION

When battery voltage reach regulation level set by VREG[4:0], the device allow charger enter termination if EN\_TERM[] = 1. In this state, when charge current falls below ITERM level, charger will be terminated after  $T_{TOPOFF}$ . After the charging cycle is completed, the BATFET turns off. The converter keeps running to power the system, and BATFET can turn on again to engage Supplement Mode.

When termination occurs, the status register CHRG\_STAT is set to 11, and an INT pulse is asserted to the host. Termination is temporarily disabled when the charger device is in input current, voltage or thermal regulation. Termination can be disabled by writing 0 to EN\_TERM bit prior to charge termination.

At low termination currents, due to the comparator offset, the actual termination current may be higher than the termination target. In order to compensate for comparator offset, a programmable top-off timer can be applied after termination is detected. The termination timer will

follow safety timer constraints, such that if safety timer is suspended, so will the termination timer. Similarly, if safety timer is doubled, so will the termination timer. TOPOFF\_ACTIVE bit reports whether the top off timer is active or not. The host can read CHRG\_STAT and TOPOFF\_ACTIVE to find out the termination status.

Top off timer gets reset at one of the following conditions:

- 1. Charge disable to enable

- 2. Termination status low to high

- 3. REG\_RST register bit is set

The top-off timer settings are read in once termination is detected by the charger. Programming a top-off timer value after termination will have no effect unless a recharge cycle is initiated. An INT is asserted to the host when entering top-off timer segment as well as when top-off timer expires.

#### CHARGE SAFETY TIMER

The device has built-in safety timer to prevent extended charging cycle due to abnormal battery conditions. The safety timer is 2 hours when the battery is below VBATLOWV threshold. The user can program fast charge safety timer through I<sup>2</sup>C (CHG\_TIMER bits). When safety timer expires, the fault register CHRG\_FAULT bits are set to 11 and an INT is asserted to the host. The safety timer feature can be disabled through I<sup>2</sup>C by setting EN\_TIMER bit.

During input voltage, current, JEITA cool or thermal regulation, the safety timer counts at half clock rate as the actual charge current is likely to be below the register setting. For example, if the charger is in input current regulation (IDPM\_STAT = 1) throughout the whole charging cycle, and the safety time is set to 5 hours, the safety timer will expire in 10 hours. This half clock rate feature can be disabled by writing 0 to TMR2X\_EN bit.

During the fault, timer is suspended. Once the fault goes away, fault resumes. If user stops the current charging cycle, and start again, timer gets reset (toggle nCE pin or CHRG\_CONFIG bit).

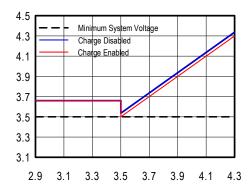

#### MINIMUM SYS VOLTAGE

Because the rail that provide power to system is SYS voltage, so to make sure the system always has enough voltage, ETA6953 provide minimum SYS voltage selection. The minimum system voltage is set by SYS\_MIN[2:0] bits. Even with a fully depleted battery, the system is regulated above the minimum system voltage (default 3.5 V).

When the battery is below minimum system voltage setting, the BATFET operates in linear mode (LDO mode), and the system is typically 180 mV above the minimum system voltage setting. As the battery voltage rises above the minimum system voltage, BATFET is fully on and the voltage difference between the system and battery is the VDS of BATFET.

When the battery charging is disabled and above minimum system voltage setting or charging is terminated, the system is always regulated at typically 70mV above battery voltage. The status register VSYS\_STAT bit goes high when the system is in minimum system voltage regulation.

Figure 3: System Voltage vs Battery Voltage

#### DYNAMIC POWER MANAGEMENT

To meet maximum current limit in USB spec and avoid over loading the adapter, the device features Dynamic Power management (DPM), which continuously monitors the input current and input voltage. When input source is over-loaded, either the current exceeds the input current limit (IINDPM) or the voltage falls below the input voltage limit (VINDPM). The device then reduces the charge current until the input current falls below the input current limit and the input voltage rises above the input voltage limit.

When the charge current is reduced to zero, but the input source is still overloaded, the system voltage starts to drop. Once the system voltage falls below the battery voltage, the device automatically enters the supplement mode where the BATFET turns on and battery starts discharging so that the system is supported from both the input source and battery.

During DPM mode, the status register bits VDPM\_STAT (VINDPM) or IDPM\_STAT (IINDPM) goes high.

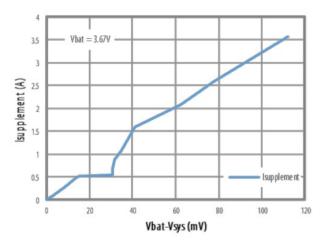

#### SUPPLEMENT MODE

When the system voltage falls 10 mV ( $V_{BAT} > V_{SYSMIN}$  when Q4 is full on. In this condition, discharge current is almost 1A.) or 20mV ( $V_{BAT} < V_{SYSMIN}$  when Q4 is in regulation. In this condition, gate of Q4 is regulated at about only threshold voltage of the FET, then discharge current is almost zero.) below the battery voltage, the BATFET turns on and the BATFET gate is regulated the gate drive of BATFET so that the minimum BATFET VDS stays at 30 mV when the current is low. This prevents oscillation from entering and exiting the supplement mode.

As the discharge current increases, the BATFET gate is regulated with a higher voltage to reduce RDSON until the BATFET is in full conduction. At this point onwards, the BATFET VDS linearly increases with discharge current. Following figure shows the V-I curve of the BATFET gate regulation operation. BATFET turns off to exit supplement mode when the battery is below battery depletion threshold.

Figure 4: BATFET Current at Entering Supplement Mode

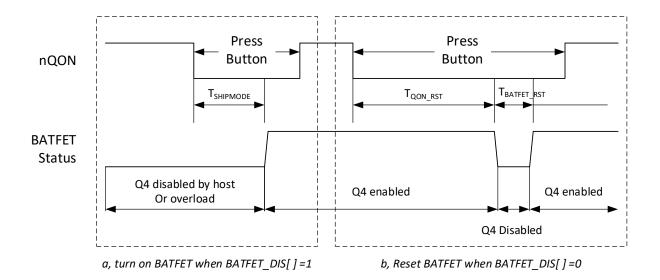

#### SHIPPING MODE AND nQON PIN

#### BATFET DISALBE MODE (SHIPPING MODE)

To extend battery life and minimize power when system is powered off during system idle, shipping, or storage, the device can turn off BATFET so that the system voltage is zero to minimize the battery leakage current. When the host set BATFET\_DIS bit, the charger can turn off BATFET immediately or delay by  $t_{\text{SM\_DLY}}$  as configured by BATFET\_DLY bit.

#### BATFET ENABLE (EXIT SHIPPING MODE)

When the BATFET is disabled (in shipping mode) and indicated by setting BATFET\_DIS, one of the following events can enable BATFET to restore system power:

- 1. Plug in adapter

- 2. Clear BATFET DIS bit

- 3. Set REG\_RST bit to reset all registers including BATFET\_DIS bit to default (0)

- 4. A logic high to low transition on nQON pin with t<sub>SHIPMODE</sub> deglitch time (1.15s typical) to enable BATFET to exit shipping mode

#### BATFET FULL SYSTEM RESET

The BATFET functions as a load switch between battery and system when input source is not plugged-in. By changing the state of BATFET from on to off, systems connected to SYS can be effectively forced to have a power-on-reset. The QON pin supports push-button interface to reset system power without host by changing the state of BATFET.

When the QON pin is driven to logic low for  $t_{QON\_RST}$  while input source is not plugged in and BATFET is enabled (BATFET\_DIS = 0), the BATFET is turned off for  $t_{BATFET\_RST}$  and then it is re-enabled to reset system power. This function can be disabled by setting BATFET RST EN bit to 0.

#### **nQON PIN OPERATION**

Internally, there is a 500K pull up resistor from nQON pin to VDD(maximum of VBAT and VLDO). So default, nQON will be high. Then nQON logic low and high voltage threshold are 0.68V and 0.88V respectively. The nQON pin incorporates two functions to control BATFET.

- BATFET Enable: A nQON logic transition from high to low with longer than t<sub>SHIPMODE</sub> deglitch turns on BATFET and exit shipping mode

- 2. BATFET Reset: When nQON is driven to logic low by at least tQON\_RST (12s typical) while adapter is not plugged in (and BATFET\_DIS = 0), the BATFET is turned off for tBATFET\_RST (10s typical). The BATFET is re-enabled after tBATFET\_RST duration. This function allows systems connected to SYS to have power-on-reset. This function can be disabled by setting BATFET\_RST\_EN bit to 0.

Figure 5: nQON Timing

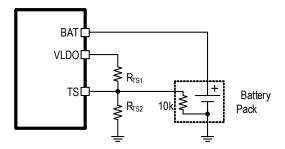

# THERMISTOR QUALIFICATION DURING CHARGING MODE

The charger device provides a single thermistor input for battery temperature monitor.

Figure 6: Thermistor Configuration

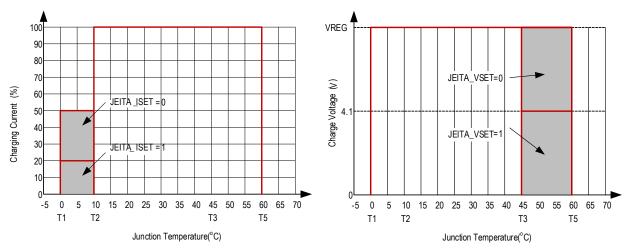

To improve the safety of charging Li-ion batteries, JEITA guideline was released on April 20, 2007. The guideline emphasized the importance of avoiding a high charge current and high charge voltage at certain low and high temperature ranges.

To initiate a charge cycle, the voltage on TS pin must be within the VT1 to VT5 thresholds. If TS voltage exceeds the T1-T5 range, the controller suspends charging and waits until the battery temperature is within the T1 to T5 range.

At cool temperature (T1-T2), JEITA recommends the charge current to be reduced to half of the charge current or lower. At warm temperature (T3-T5), JEITA recommends charge voltage less than 4.1V.

The charger provides flexible voltage/current settings beyond the JEITA requirement. The voltage setting at warm temperature (T3-T5) can be VREG or 4.1V (configured by JEITA\_VSET). The current setting at cool temperature (T1-T2) can be further reduced to 20% of fast charge current (JEITA\_ISET).

Figure 7: JEITA Profile: Charging Current

Figure 8: JEITA Profile: Charging Voltage

The resistor bias network has been updated as below.

$$RTS1 = \frac{\left(\frac{\text{VLDO}}{\text{VT1}} - 1\right)}{\frac{1}{\text{RTS2}} + \frac{1}{\text{RTH}_{COLD}}} \qquad RTS2 = \frac{\text{VLDO} \times \text{RTH}_{COLD} \times \text{RTH}_{HOT} \times \left(\frac{1}{\text{VT1}} - \frac{1}{\text{VT5}}\right)}{\text{RTH}_{HOT} \times \left(\frac{\text{VLDO}}{\text{VT5}} - 1\right) - \text{RTH}_{COLD} \times \left(\frac{\text{VLDO}}{\text{VT1}} - 1\right)}$$

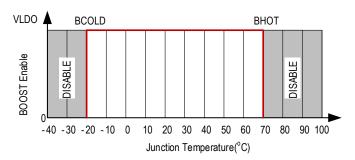

#### THERMISTOR QUALIFICATION DURING BATTERY DISCHARGE MODE

For battery protection during boost mode, the device monitors the battery temperature to be within the VBCOLD to VBHOT thresholds. When temperature is outside of the temperature thresholds, the boost mode is suspended. in additional, VBUS\_STAT bits are set to 000 and NTC\_FAULT is reported. Once temperature returns within thresholds, the boost mode is recovered and NTC\_FAULT is cleared.

Figure 9: TS Pin Thermistor Sense Threshold in Boost Mode

#### INDICATION OUTPUT

#### POWER GOOD INDICATION ON nPG PIN OR PG\_STAT BIT

The PG\_STAT bit goes HIGH and nPG pin goes LOW to indicate a good input source when:

- VBUS Pass Poor Source Detection

- Completed input Source Type Detection

#### CHARGING STATUS INDICATION ON STAT PIN

The device indicates charging state on the open drain STAT pin. The STAT pin can drive LED. The STAT pin function can be disabled by setting the STAT CONFIG[1:0] = 11. When STAT CONFIG[1:0] = 00, STAT indication operates as shown as in below table.

Table 2: STAT Indication table

| CHARGE STATE                                                                                                          | STAT INDICATION                          |

|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------|

| Charging in progress (including recharge)                                                                             | LOW                                      |

| Charging complete                                                                                                     | HIGH                                     |

| Sleep mode, charge disable                                                                                            | HIGH                                     |

| Charge suspend (input overvoltage, TS fault, timer fault or system overvoltage)  Boost Mode suspend (due to TS fault) | Blinking at 1Hz<br>(0.5s LOW / 0.5s HIZ) |

#### HOST INTERRUPT ON NINT PIN

ETA6953 provides a comfortable feature that host does not need to always monitor the charger operation. The nINT pulse notifies the system on the device operation. The following events will generate 256-µs INT pulse.

- > Input Source Type Detection Completed (through PSEL detection)

- VBUS Pass Poor Source Detection

- Input removed

- Charge Complete

- > Any FAULT event in REG09

- > VINDPM event detected. Masked by VINDPM\_INT\_ MASK = 1.

- > IINDPM event detected. Masked by IINDPM\_INT\_ MASK = 1.

When a fault occurs, the charger device sends out nINT and keeps the fault state in REG09 until the host reads the fault register. Before the host reads REG09 and all the faults are cleared, the charger device would not send any INT upon new faults. To read the current fault status, the host has to read REG09 two times consecutively. The first read reports the pre-existing fault register status and the second read reports the current fault register status.

#### INPUT OVERVOLTAGE PROTECTION IN CHARGE MODE (ACOV)

If VBUS voltage exceeds the VBUS over voltage threshold VBUS\_OV (programmable via OVP[1:0] bits) the device stops switching immediately. During input overvoltage event, the fault register CHRG\_FAULT bits are set to 01. An INT pulse is asserted to the host. The device will automatically resume normal operation once the input voltage drops back below the OVP threshold.

#### SYSTEM OVERVOLTAGE PROTOECTION IN CHARGE MODE (SYSOVP)

The charger device clamps the system voltage during load transient so that the components connect to system would not be damaged due to high voltage. SYSOVP threshold is 14% above system regulation voltage. Upon SYSOVP, converter stops immediately to clamp the overshoot.

#### VBUS OUTPUT SHORT PROTECTION IN BOOST MODE

The device monitors boost output voltage and other conditions to provide output short circuit and overvoltage protection. The Boost build-in accurate constant current regulation to allow OTG to adaptive to various types of load. If short circuit is detected on VBUS, the Boost turns off and retry 7 times. If retries are not successful, OTG is disabled with OTG\_CONFIG bit cleared. In addition, the BOOST\_FAULT bit is set and INT pulse is generated. The BOOST\_FAULT bit can be cleared by host by re-enabling boost mode

#### VBUS OVERVOLTAGE PROTECTION IN BOOST MODE

When the VBUS voltage rises above regulation target and exceeds the over voltage threshold VOTG\_OVP, the device enters overvoltage protection which stops switching, clears OTG\_CONFIG bit and exits boost mode. At Boost overvoltage duration, the fault register bit (BOOST\_FAULT) is set high to indicate fault in boost operation. An INT is also asserted to the host.

#### THERMAL REGULATION IN BUCK MODE

The ETA6953 monitors the internal junction temperature T<sub>J</sub> to avoid overheat the chip and limits the IC surface temperature at 110°C in buck mode. When the internal junction temperature exceeds thermal regulation limit (110°C), the device lowers down the charge current. During thermal regulation, the actual charging current is usually below the programmed battery charging current. Therefore, termination is disabled, the safety timer runs at half the clock rate, and the status register THERM\_STAT bit goes high.

Thermal limit is programmable to 90°C by programming TREG bit.

#### THERMAL SHUTDOWN

The device monitors the internal junction temperature to provide thermal shutdown during any mode. When IC surface temperature exceeds TSHUT (160°C) BATFET and Converter are disabled. OTG\_CONFIG bit is cleared if in BOOST mode and BOOST\_FAULT bit is set. In Charge mode, CHARGE\_FAULT bit is set. An nINT pulse is asserted to the host.

When IC temperature is  $T_{SHUT\_HYS}$  (30°C) below  $T_{SHUT}$  (160°C), The BATFET and charger are enabled following enable condition, Boost can be enabled by host.

#### **BATTERY OVER-VOLTAGE PROTECTION**

The battery overvoltage limit is clamped at 7% above the battery regulation voltage. When battery over voltage occurs, the charger device immediately disables charge. The fault register BAT\_FAULT bit goes high and an INT is asserted to the host

#### BATTERY OVER-DISCHARGE PROTECTION

When battery is discharged below the battery depletion falling threshold V<sub>BAT\_DPL\_FALL</sub>, the BATFET is turned off to protect battery from over discharge. To recover from over-discharge, an input source is required at VBUS. When an input source is plugged in, the BATFET turns on. The battery is charged with I<sub>SHORT</sub> (typically 150 mA) current when the VBAT is smaller than the trickle charge voltage threshold V<sub>SHORT</sub>, or pre-charge current as set in I<sub>PRECHG</sub> register when the battery voltage is between V<sub>SHORT</sub> and the pre-charge voltage threshold V<sub>BAT LOWV</sub>.

#### SYSTEM OVER-CURRENT PROTECTION

When the system is shorted or significantly overloaded (I<sub>BAT</sub> > I<sub>BATOP</sub>) so that its current exceeds the overcurrent limit, the device latches off BATFET. Section BATFET Enable (Exit Shipping Mode) can reset the latch-off condition and turn on BATFET.

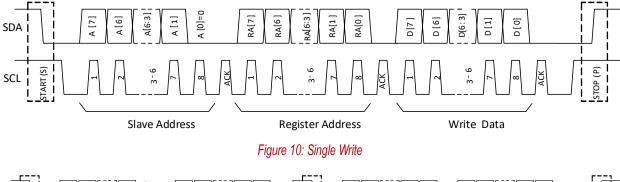

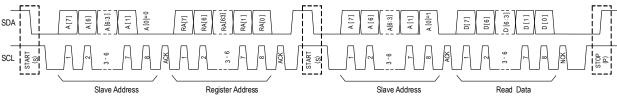

#### 12C COMMUNICATION

The device uses I²C compatible interface for flexible charging parameter programming and instantaneous device status reporting. I²C™ is a bi-directional 2-wire serial interface developed by Philips Semiconductor (now NXP Semiconductors). Only two bus lines are required: a serial data line (SDA) and a serial clock line (SCL). Devices can be considered as masters or slaves when performing data transfers. A master is the device which initiates a data transfer on the bus and generates the clock signals to permit that transfer. At that time, any device addressed is considered a slave.

The device operates as a slave device with address D6H, receiving control inputs from the master device like micro controller or a digital signal processor through REG00-REG0C. The I<sup>2</sup>C interface supports both standard mode (up to 100kbits), and fast mode (up to 400kbits), connecting to the positive supply voltage via a current source or pull-up resistor. When the bus is free, both lines are HIGH. The SDA and SCL pins are open drain.

Figure 11: Singe Read

Device address is understood value of A[7:0] while A[0] is "0". This is also the address to write the data to the device registers. To read data from register, sending the command to address with A[0] is "1". Register address are in RA[7:0]. Data to or from register are D[7:0].

## **REGISTER MAP**

Table 3: REG00

| BIT | NAME           | POR | TYPE | RESET BY    | DESCRIPTION             | NOTE                                       |

|-----|----------------|-----|------|-------------|-------------------------|--------------------------------------------|

| 7   | EN_HIZ         | 0   | R/W  | by REG_RST  | 0-Disable, 1-Enable     | Enable HIZ Mode                            |

|     |                |     |      | by Watchdog |                         | 0-Disable (default)                        |

|     |                |     |      |             |                         | 1-Enable                                   |

| 6   | EN_ICHG_MON[1] | 0   | R/W  | by REG_RST  | 00 - Enable STAT        |                                            |

| 5   | EN_ICHG_MON[0] | 0   |      |             | pin function(default)   |                                            |

|     |                |     |      |             | 01 - Reserved           |                                            |

|     |                |     |      |             | 10 - Reserved           |                                            |

|     |                |     |      |             | 11 - Disable STAT       |                                            |

|     |                |     |      |             | pin function(float pin) |                                            |

| 4   | IINDPM[4]      | 1   | R/W  | by REG_RST  | 1600 mA                 | Input Current Limit                        |

| 3   | IINDPM[3]      | 0   | R/W  | by REG_RST  | 800 mA                  | Offset: 100 mA                             |

| 2   | IINDPM[2]      | 1   | R/W  | by REG_RST  | 400 mA                  | Range: 100 mA (000000) – 3.2 A (11111)     |

| 1   | IINDPM[1]      | 1   | R/W  | by REG_RST  | 200 mA                  | Default:2400 mA (10111),                   |

| 0   | IINDPM[0]      | 1   | R/W  | by REG_RST  | 100 mA                  | maximum input current limit, not typical.  |

|     |                |     |      |             |                         | IINDPM bits are changed                    |

|     |                |     |      |             |                         | automatically after input source detection |

|     |                |     |      |             |                         | is completed                               |

|     |                |     |      |             |                         | PSEL = Hi = 500 mA                         |

|     |                |     |      |             |                         | PSEL = Lo = 2.4 A                          |

|     |                |     |      |             |                         | Host can over-write IINDPM register bits   |

|     |                |     |      |             |                         | after input source detection is completed. |

### Table 4: REG01

| BIT | NAME       | POR | TYPE | RESET BY    | DESCRIPTION                           | NOTE                                     |

|-----|------------|-----|------|-------------|---------------------------------------|------------------------------------------|

| 7   | PFM_DIS    | 0   | R/W  | by REG_RST  | 0 – Enable PFM                        | Default: 0 - Enable                      |

|     |            |     |      |             | 1 – Disable PFM                       |                                          |

| 6   | WD_RST     | 0   | R/W  | by REG_RST  | I <sup>2</sup> C Watchdog Timer Reset | Default: Normal (0) Back to 0 after      |

|     |            |     |      | by Watchdog | 0 –Normal; 1 – Reset                  | watchdog timer reset                     |

| 5   | OTG_CONFIG | 0   | R/W  | by REG_RST  | 0 – OTG Disable                       | Default: OTG disable (0)                 |

|     |            |     |      | by Watchdog | 1 – OTG Enable                        | Note:                                    |

|     |            |     |      |             |                                       | 1. OTG_CONFIG would over-ride            |

|     |            |     |      |             |                                       | Charge Enable Function in                |

|     |            |     |      |             |                                       | CHG_CONFIG                               |

| 4   | CHG_CONFIG | 1   | R/W  | by REG_RST  | 0 - Charge Disable                    | Default: Charge Battery (1)              |

|     |            |     |      | by Watchdog | 1- Charge Enable                      | Note:                                    |

|     |            |     |      |             |                                       | 1. Charge is enabled when both CE pin is |

|     |            |     |      |             |                                       | pulled low AND                           |

|     |            |     |      |             |                                       | CHG_CONFIG bit is 1.                     |

#### Table 4: REG01

| BIT | NAME         | POR | TYPE | RESET BY   | DESCRIPTION            |                   | NOTE                        |

|-----|--------------|-----|------|------------|------------------------|-------------------|-----------------------------|

| 3   | SYS_Min[2]   | 1   | R/W  | by REG_RST | System Minimum Voltage | 000: 2.6 V        | 001: 2.8 V                  |

| 2   | SYS_Min[1]   | 0   | R/W  | by REG_RST |                        | 010: 3 V          | 011: 3.2 V                  |