# SGM56101Q 110dB, 192kHz, 32-Bit, 8-Channel Audio DAC for Automotive Applications

#### GENERAL DESCRIPTION

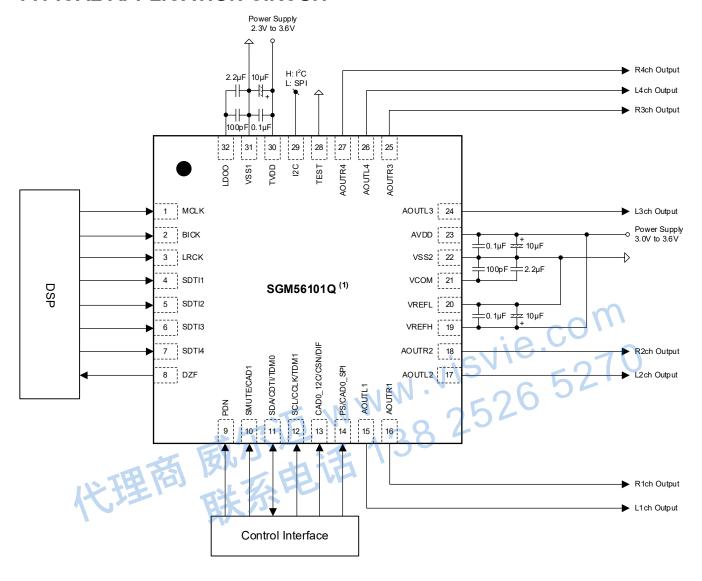

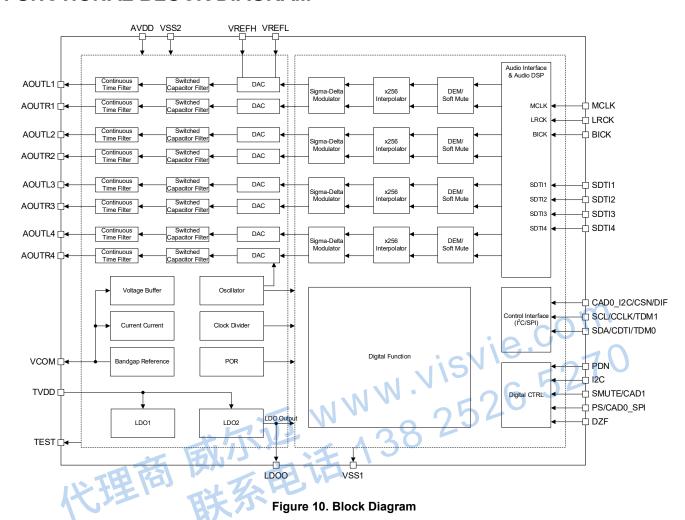

The SGM56101Q is an 8-channel, 32-bit DAC designed for digital audio systems. Its internal circuitry boasts a state-of-the-art 32-bit digital filter that optimizes both audio quality and short group delay. With support for a maximum 192kHz PCM input, it is ideal for reproducing high-resolution audio sources that are increasingly common in network audios, USB-DACs and car audio systems.

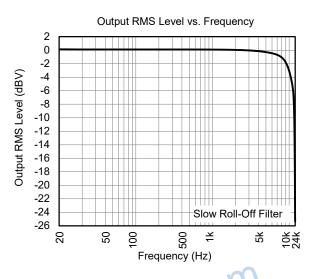

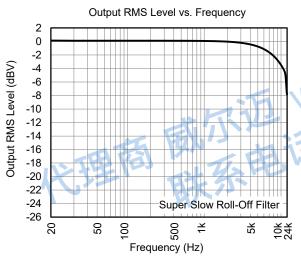

Furthermore, the SGM56101Q incorporates the innovative OSR-doubler technology, enabling it to handle a diverse range of signals while minimizing out-of-band noise and maintaining low power consumption. Additionally, the device provides three types of 32-bit digital filters, which can enable sound making simple and flexible in wide range of applications. It should be noted that SGM56101Q needs to input the MCLK signal in advance to execute the 3-wire serial/I<sup>2</sup>C-bus program.

The device is AEC-Q100 qualified (Automotive Electronics Council (AEC) standard Q100 Grade 1) and it is suitable for automotive applications.

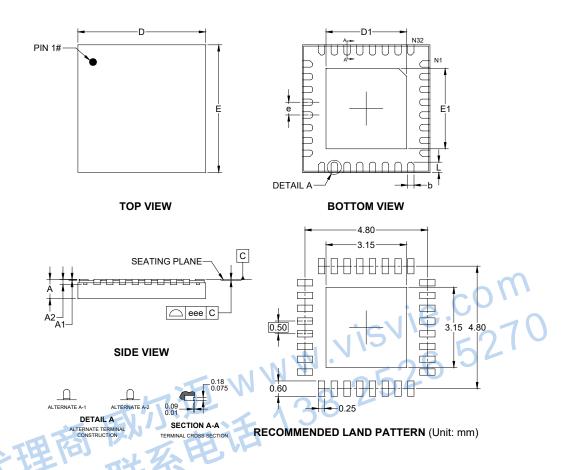

The SGM56101Q is available in a Green TQFN-5×5-32FL package.

#### **APPLICATIONS**

Automotive Applications

External Amplifiers

Car Audios System

CD Players

Headphones

Network Audios (Audio-Over-IP)

Professional Measuring Instruments

RCA Receivers

Super Audio CD Players

USB DACs

#### **FEATURES**

- AEC-Q100 Qualified for Automotive Applications

Device Temperature Grade 1

T<sub>A</sub> = -40°C to +125°C

- Power Supply Voltage Range

- Analog Power Supply: AVDD = 3.0V to 3.6V

- Digital Power Supply: TVDD = 2.3V to 3.6V

- Digital Power Supply with Integrated LDO

- 32-Bit, 8-Channel DAC

- x256 Oversampling

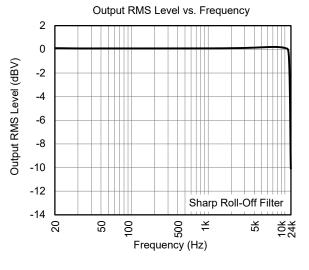

- 32-Bit, High-Performance Sound Digital Filter

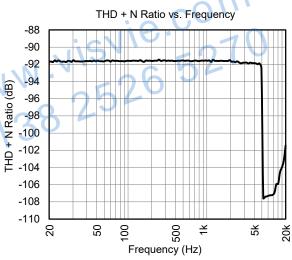

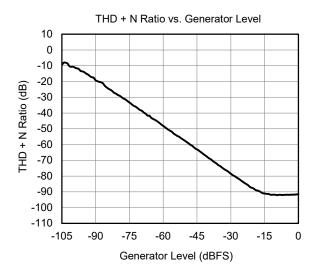

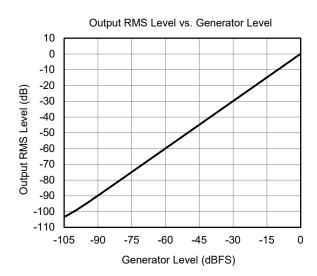

- THD + N: 91.5dB

- DR, SNR: 110dB

- Flexible Digital Volume Control System (Each Channel): Full Range 0dB to -127dB, 0.5dB per Step and Mute

- Soft Mute

- De-emphasis Filter Options: 32kHz, 44.1kHz and 48kHz

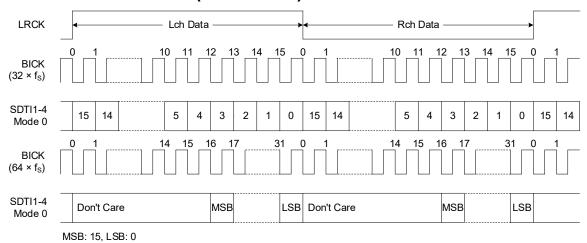

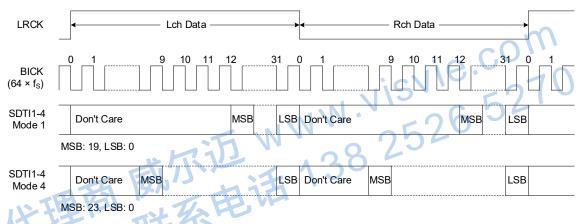

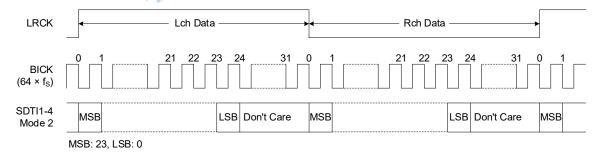

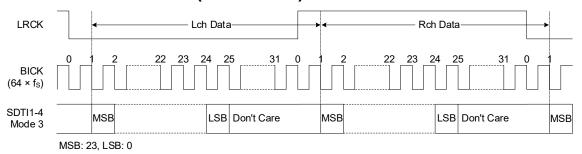

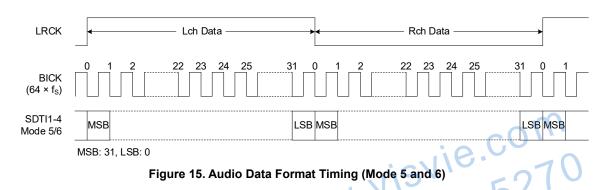

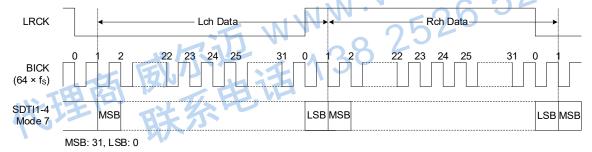

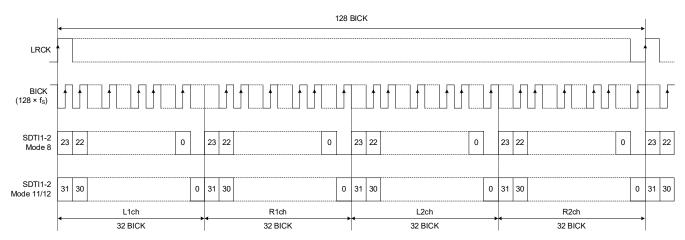

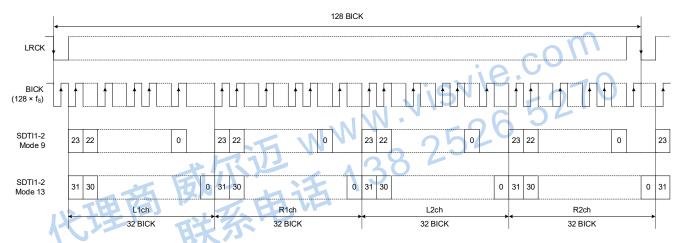

- Audio Interface Format Options:

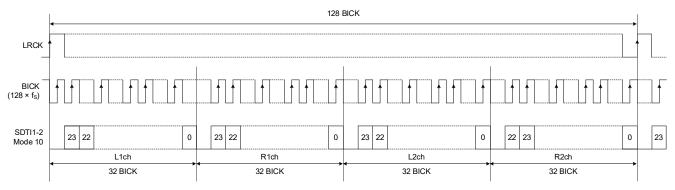

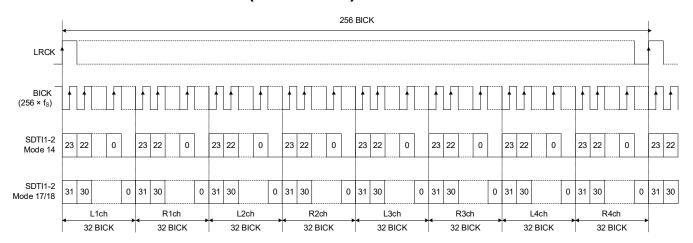

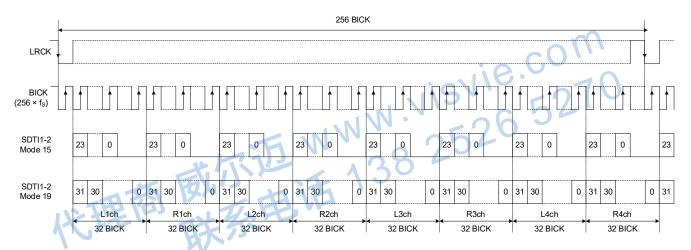

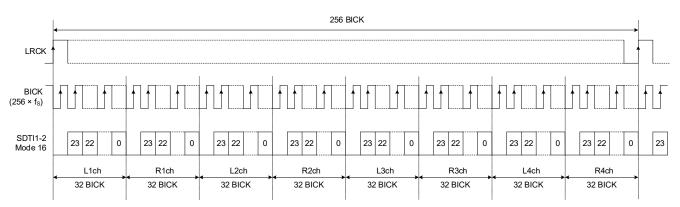

MSB/LSB Justified, I<sup>2</sup>S and TDM

- Channel-Independent Zero Detection

- Sampling Frequency

- Normal Speed Mode: f<sub>S</sub> = 8kHz to 48kHz

- Double Speed Mode: f<sub>S</sub> = 48kHz to 96kHz

- Quad Speed Mode: f<sub>S</sub> = 96kHz to 192kHz

- Master Clock Ratio

- Normal Speed Mode: 256 × f<sub>S</sub>, 384 × f<sub>S</sub>, 512 × f<sub>S</sub>, 768 × f<sub>S</sub>

- Double Speed Mode: 128 × f<sub>S</sub>, 192 × f<sub>S</sub>, 256 × f<sub>S</sub>

- Quad Speed Mode: 128 × f<sub>S</sub>

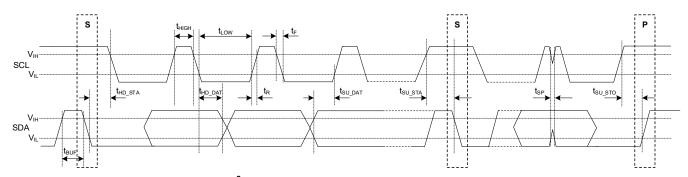

- Control Interface: 3-Wire Serial, I<sup>2</sup>C-Bus (Fast Speed Mode: 400kHz) and Parallel Mode

- Operating Power Consumption: 30.5mA (f<sub>s</sub> = 48kHz)

- -40°C to +125°C Operating Temperature Range

- Available in a Green TQFN-5×5-32FL Package

### PACKAGE/ORDERING INFORMATION

| MODEL     | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING         | PACKING<br>OPTION   |

|-----------|------------------------|-----------------------------------|--------------------|----------------------------|---------------------|

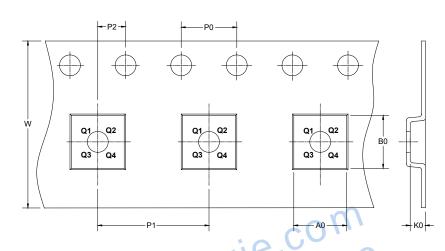

| SGM56101Q | TQFN-5×5-32FL          | -40°C to +125°C                   | SGM56101QTUP32G/TR | 0URTUP32<br>XXXXX<br>XX#XX | Tape and Reel, 3000 |

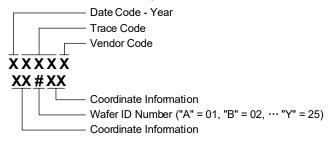

#### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code. XX#XX = Coordinate Information and Wafer ID Number.

Green (RoHS & HSF): SG Micro Corp defines Green to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

### ABSOLUTE MAXIMUM RATINGS (1)

| Power Supply Voltage Range (2) (3)                                  |   |

|---------------------------------------------------------------------|---|

| AVDD0.3V to 4.3                                                     | V |

| TVDD0.3V to 4.3                                                     | V |

| Difference (VSS1 - VSS2)0.3V to 0.3                                 | V |

| Digital Input Voltage Range, V <sub>IND</sub> (4)0.3V to TVDD + 0.3 | V |

| Input Current (Except for Supply Pins), I <sub>IN</sub> ±10m        | Α |

| Package Thermal Resistance                                          | 3 |

| TQFN-5×5-32FL, θ <sub>JA</sub>                                      |   |

| TQFN-5×5-32FL, θ <sub>JB</sub>                                      | ٧ |

| TQFN-5×5-32FL, θ <sub>JC (TOP)</sub>                                | ٧ |

| TQFN-5×5-32FL, θ <sub>JC (BOT)</sub>                                | ٧ |

| Junction Temperature+150°C                                          | С |

| Storage Temperature Range65°C to +150°C                             | С |

| Lead Temperature (Soldering, 10s)+260°0                             | С |

#### RECOMMENDED OPERATING CONDITIONS

| Power Supply Voltage Range (2) | ) (3)                    |

|--------------------------------|--------------------------|

| AVDD                           | 3.0V to 3.6V, 3.3V (TYP) |

| TVDD                           | 2.3V to 3.6V, 3.3V (TYP) |

| Voltage Reference (5)          |                          |

| High Voltage Reference, VREF   | H AVDD - 0.5V to AVDD    |

| Low Voltage Reference, VREF    | LVSS2 (TYP)              |

| Operating Ambient Temperature  | e Range40°C to +125°C    |

|                                |                          |

#### NOTES:

1. All voltages referenced to ground, VSS1 and VSS2 should be connected to a unified analog ground plane, ensuring that VSS1 and VSS2 both equal 0V.

- 2. The sequence of powering up AVDD and TVDD is not crucial for operation.

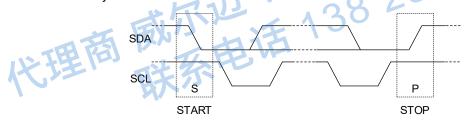

- 3. Avoid powering off the SGM56101Q while the peripheral device remains powered on. Additionally, when utilizing the I<sup>2</sup>C interface, ensure that pull-up resistors for the SDA and SCL pins are connected to TVDD or a lower voltage.

- 4. The maximum permissible digital input voltage is the smaller value between TVDD + 0.3V and 4.3V.

- 5. It is imperative to connect the VREFL pin to VSS2.

#### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

#### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

#### DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

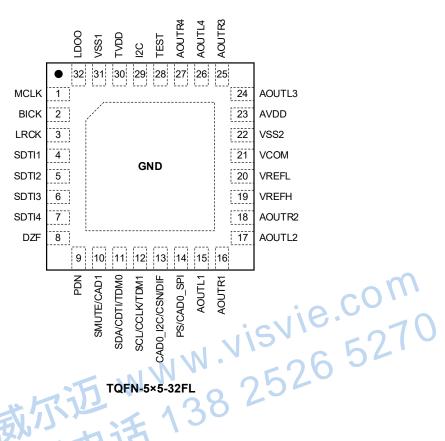

### **PIN CONFIGURATION**

### (TOP VIEW)

# PIN DESCRIPTION

|     |                | 4 3/3 |                     | 410                                                                                                                                                                                                                                                      |

|-----|----------------|-------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN | NAME           | TYPE  | POWER-DOWN<br>STATE | FUNCTION                                                                                                                                                                                                                                                 |

| 1   | MCLK           | 1     | Hi-Z                | Master Clock Input Pin (External).                                                                                                                                                                                                                       |

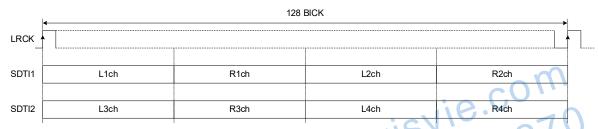

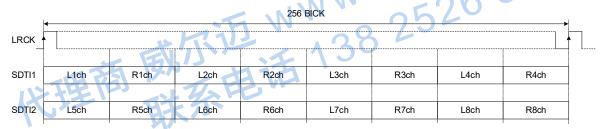

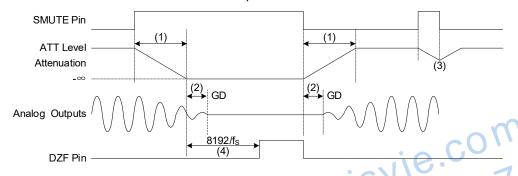

| 2   | BICK           | 1     | Hi-Z                | Serial Audio Input Bit Clock Pin.                                                                                                                                                                                                                        |

| 3   | LRCK           | 1     | Hi-Z                | Serial Audio Input Left/Right Clock Pin.                                                                                                                                                                                                                 |

| 4   | SDTI1          | 1     | Hi-Z                | Serial Audio Input Data Port.                                                                                                                                                                                                                            |

| 5   | SDTI2          | I     | Hi-Z                | Serial Audio Input Data Port.                                                                                                                                                                                                                            |

| 6   | SDTI3          | I     | Hi-Z                | Serial Audio Input Data Port.                                                                                                                                                                                                                            |

| 7   | SDTI4          | I     | Hi-Z                | Serial Audio Input Data Port.                                                                                                                                                                                                                            |

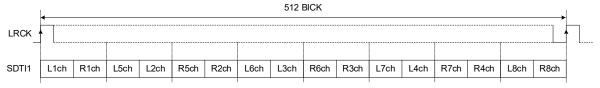

| 8   | DZF            | 0     | 50kΩ<br>Pull-Down   | Zero Detection Function Pin. When the input data of each channel reaches zero continuously within 8192 LRCK cycles, the DZF pin becomes high. When the input data of each channel does not reach zero, the DZF pin immediately reverts to the low level. |

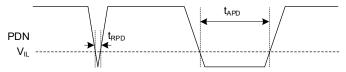

| 9   | PDN            | I     | Hi-Z                | Power-Down Pin. When it is low, the SGM56101Q enters a power-down mode, and its control registers revert to their default settings.                                                                                                                      |

| 10  | SMUTE          | I     | <b>⊔</b> i 7        | Soft Mute Pin in Parallel Control Mode. When SMUTE pin becomes high, the soft mute cycle is activated. When returning low, the output mute is released.                                                                                                  |

| 10  | 10 CAD1 I Hi-Z |       | 1 II-Z              | Chip Address 1 Pin in the I <sup>2</sup> C-Bus or 3-Wire Serial Control Mode. It serves as an identifier for the specific chip or device being addressed.                                                                                                |

|     | SDA            | I/O   |                     | Control I/O Data Line in I <sup>2</sup> C-Bus Mode.                                                                                                                                                                                                      |

| 11  | CDTI           | 1     | Hi-Z                | Output Data Pin. It is from the control port interface in 3-wire serial control mode.                                                                                                                                                                    |

|     | TDM0 I         |       |                     | Function Pin 0. It is used as the selector for the TDM mode in the parallel control mode.                                                                                                                                                                |

# **PIN DESCRIPTION (continued)**

| PIN            | NAME     | TYPE | POWER-<br>DOWN STATE | FUNCTION                                                                                                                                             |

|----------------|----------|------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

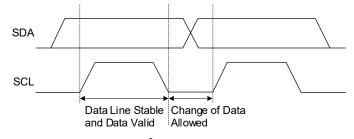

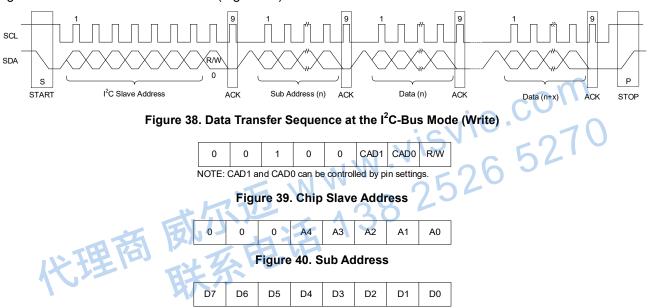

|                | SCL      | ı    |                      | Serial Control Interface Clock Pin in I <sup>2</sup> C-Bus Serial Control Mode. It is used to clock control data bits into and out of the SGM56101Q. |

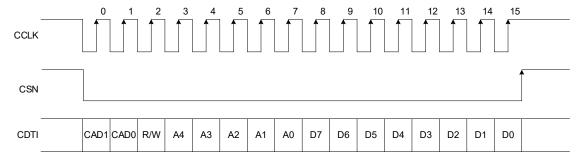

| 12             | CCLK     | I    | Hi-Z                 | Serial Control Interface Clock in 3-Wire Serial Control Mode. It is used to clock control data bits into the SGM56101Q.                              |

|                | TDM1     | I    |                      | Function Pin 1. It is used as the selector for the TDM mode in the parallel control mode.                                                            |

|                | CAD0_I2C | I    |                      | Chip Address 0 Pin in the I <sup>2</sup> C-Bus Mode. It serves as an identifier for the specific chip or device being addressed.                     |

| 13             | CSN      | I    | Hi-Z                 | Control Port Enable Pin in 3-Wire Serial Control Mode. It is used to enable the control port interface on the SGM56101Q.                             |

|                | DIF      | I    |                      | Audio Data Format Select Pin in Parallel Control Mode. Low: 32-bit MSB. High: 32-bit l <sup>2</sup> S.                                               |

| 14             | PS       | I    | Hi-Z                 | Control Mode Select Pin (I2C Pin = High). Low: I <sup>2</sup> C-bus serial control mode. High: parallel control mode.                                |

| 14             | CAD0_SPI | 1    | ПІ-Д                 | Chip Address 0 Pin (I2C Pin = Low) in 3-Wire Serial Control Mode. It serves as an identifier for the specific chip or device being addressed.        |

| 15             | AOUTL1   | 0    | Hi-Z                 | Left Channel Analog Output Pin.                                                                                                                      |

| 16             | AOUTR1   | 0    | Hi-Z                 | Right Channel Analog Output Pin.                                                                                                                     |

| 17             | AOUTL2   | 0    | Hi-Z                 | Left Channel Analog Output Pin.                                                                                                                      |

| 18             | AOUTR2   | 0    | Hi-Z                 | Right Channel Analog Output Pin.                                                                                                                     |

| 19             | VREFH    | _    | Hi-Z                 | High Voltage Reference Input Pin. It should be connected to the AVDD.                                                                                |

| 20             | VREFL    | _    | Hi-Z                 | Low Voltage Reference Input Pin. It should be connected to the VSS2.                                                                                 |

| 21             | VCOM     | 0    | 500Ω<br>Pull-Down    | Common Voltage Output Pin (AVDD × 1/2). Use a large external capacitor around 2.2µF to reduce power noise.                                           |

| 22             | VSS2     | -    | * 137                | Analog Ground Pin. Ground for the analog circuitry in the chip.                                                                                      |

| 23             | AVDD     | · ·  | <b>包</b> 为一个         | Analog Power Supply Pin. The voltage range is from 3.0V to 3.6V.                                                                                     |

| 24             | AOUTL3   | 0    | Hi-Z                 | Left Channel Analog Output Pin.                                                                                                                      |

| 25             | AOUTR3   | 0    | Hi-Z                 | Right Channel Analog Output Pin.                                                                                                                     |

| 26             | AOUTL4   | 0    | Hi-Z                 | Left Channel Analog Output Pin.                                                                                                                      |

| 27             | AOUTR4   | 0    | Hi-Z                 | Right Channel Analog Output Pin.                                                                                                                     |

| 28             | TEST     | _    | 21.5kΩ<br>Pull-Down  | TEST pin. It should be connected to VSS1.                                                                                                            |

| 29             | I2C      | I    | Hi-Z                 | Control Mode Select Pin. Low: 3-wire serial control mode. High: I <sup>2</sup> C-bus serial control mode or parallel control mode.                   |

| 30             | TVDD     | Р    | _                    | Digital Power Supply Pin. The voltage range is from 2.3V to 3.6V.                                                                                    |

| 31             | VSS1     | _    | _                    | Digital Ground Pin.                                                                                                                                  |

| 32             | LDOO     | 0    | 630Ω<br>Pull-Down    | LDO Output Pin. The pin requires a connection to ground via a 2.2uF capacitor with a tolerance of ±50%.                                              |

| Exposed<br>Pad | GND      | -    | _                    | The exposed pad on the bottom surface of the package should be connected to the ground plane for optimized heat dissipation.                         |

- 1. I = input, O = output, I/O = input or output, P = power.

- 2. All digital inputs must be securely connected and not allowed to remain unconnected or floating.

#### **ELECTRICAL CHARACTERISTICS**

(AVDD = TVDD = VREFH = 3.3V, VSS1 = VSS2 = 0V, T<sub>A</sub> = +25°C, unless otherwise noted.) (1)

| PARAMETER                                 | SYMBOL                                                        | С                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ONDITIONS                             | MIN | TYP  | MAX | UNITS |

|-------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----|------|-----|-------|

| DAC Analog Output                         |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       | •   |      | •   |       |

| Resolution                                |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |     | 32   |     | Bits  |

| Output Voltage (2)                        |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |     | 2.8  |     | Vpp   |

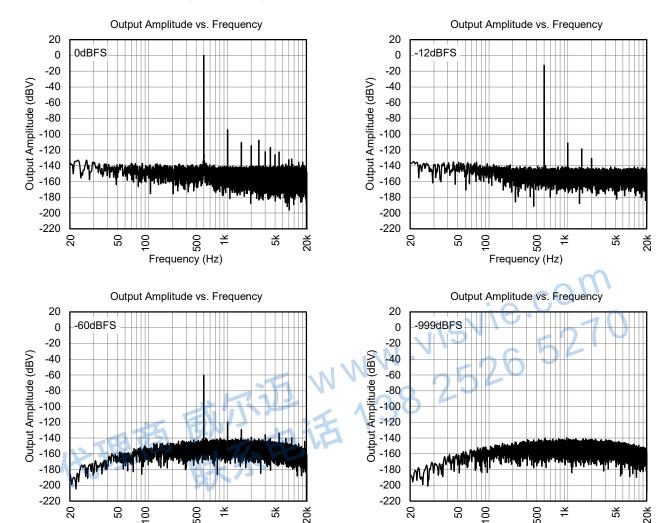

|                                           |                                                               | f <sub>S</sub> = 48kHz <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       |     | 91.5 |     |       |

| Total Harmonic Distortion + Noise (0dBFS) | THD + N                                                       | f <sub>S</sub> = 96kHz <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                       |     | 90   |     | dB    |

| (                                         |                                                               | f <sub>S</sub> = 192kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       |     | 86   |     |       |

|                                           |                                                               | f <sub>S</sub> = 48kHz (A-weig                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | hted)                                 |     | 110  |     |       |

| Dynamic Range (-60dBFS)                   | DR                                                            | f <sub>S</sub> = 96kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                       |     | 103  |     | dB    |

|                                           |                                                               | f <sub>S</sub> = 192kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       |     | 102  |     |       |

|                                           |                                                               | f <sub>S</sub> = 48kHz (A-weig                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | hted)                                 |     | 110  |     |       |

| Signal to Noise Ratio                     | SNR                                                           | f <sub>S</sub> = 96kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                       |     | 103  |     | dB    |

|                                           |                                                               | f <sub>S</sub> = 192kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       |     | 103  |     |       |

| Interchannel Isolation                    |                                                               | Isolation from other LR channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                       |     | 109  |     | dB    |

| interchanner isolation                    |                                                               | Isolation of LR for a single channel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                       |     | 105  | 2   |       |

| Interchannel Gain Mismatch                |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |     | 0    |     | dB    |

| Load Resistance (4)                       | $R_L$                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                     | 16. | 5/10 | 10  | kΩ    |

| Load Capacitance                          | $C_L$                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 115 <sup>V</sup>                      |     | 40   |     | pF    |

|                                           |                                                               | AVDD (5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                       | 26  | 65   | •   |       |

| Power Supply Rejection                    | PSR                                                           | TVDD (6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | W " 06'                               |     | 88   |     | dB    |

|                                           |                                                               | VREFH (7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 00 73                                 |     | 82   |     |       |

| Power Supply                              |                                                               | The same of the sa | 1.30                                  |     |      |     |       |

| 77 75                                     | I <sub>AVDD</sub>                                             | 一出话                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | f <sub>S</sub> = 48kHz, 96kHz, 192kHz |     | 14   |     |       |

| Power Supply Current                      | 147                                                           | YES W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | f <sub>S</sub> = 48kHz                |     | 14   |     |       |

|                                           | I <sub>TVDD</sub>                                             | Normal operation (PDN pin = high)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | f <sub>S</sub> = 96kHz                |     | 25   |     | mA    |

|                                           |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | f <sub>S</sub> = 192kHz               |     | 35   |     |       |

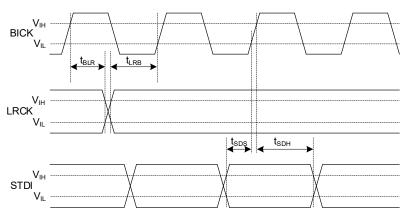

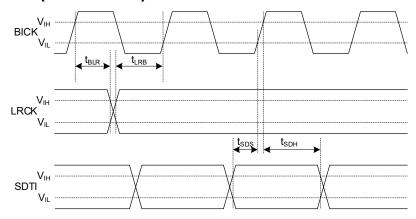

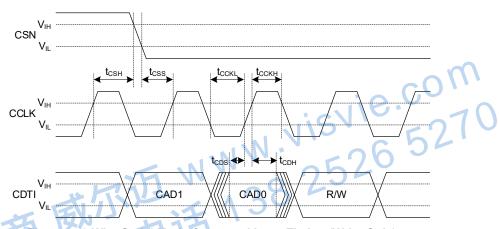

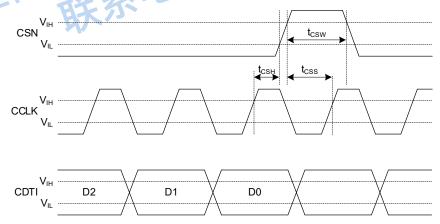

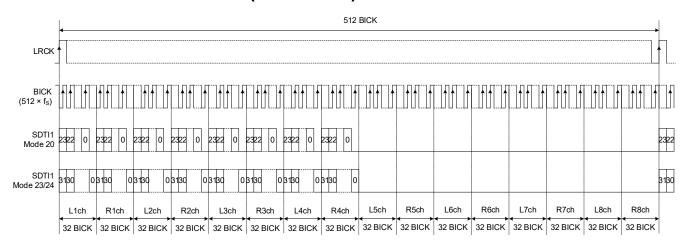

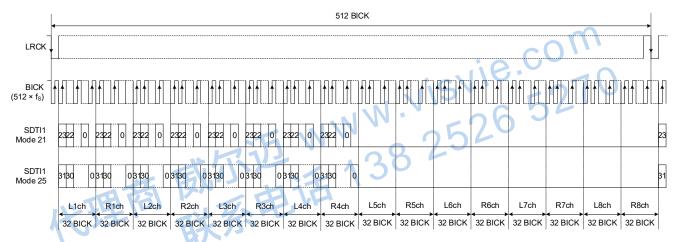

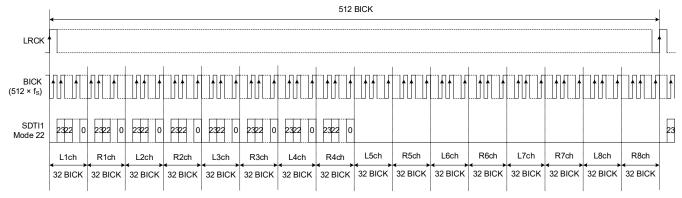

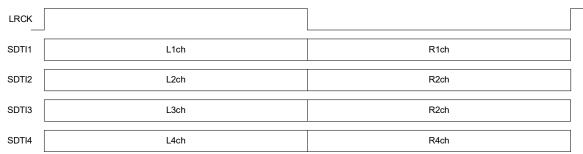

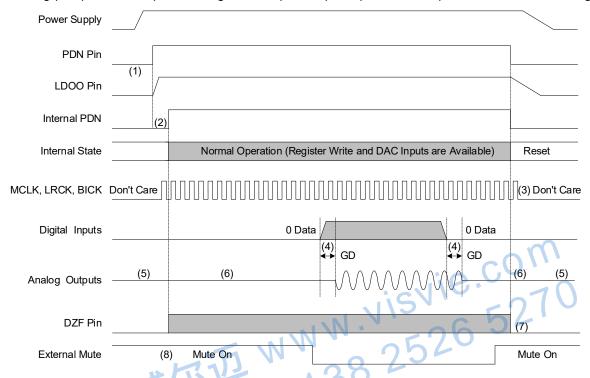

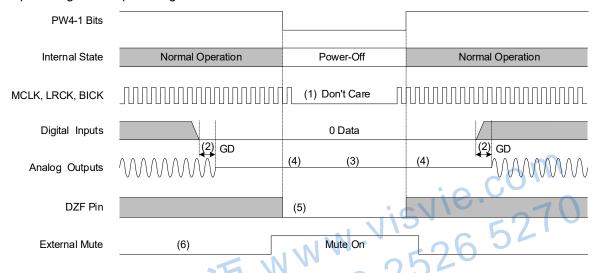

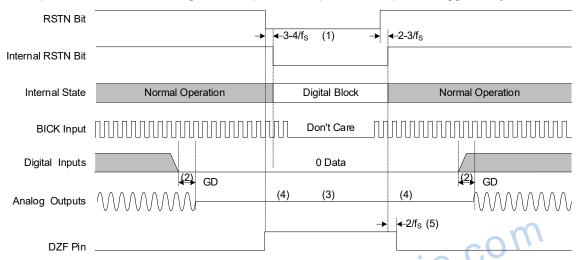

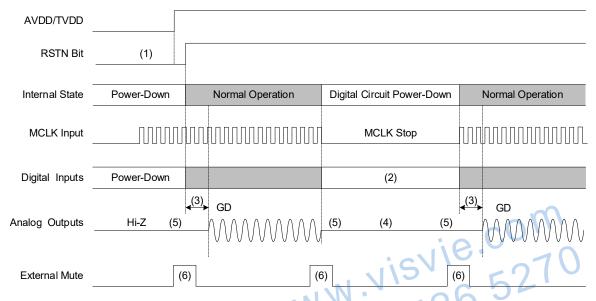

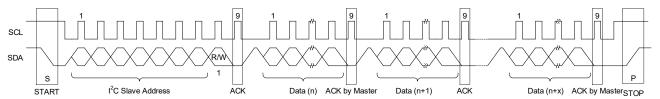

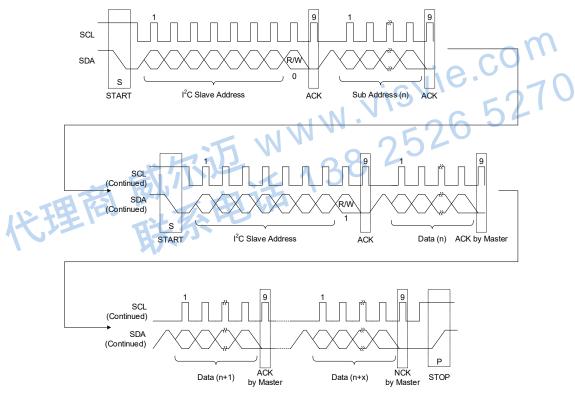

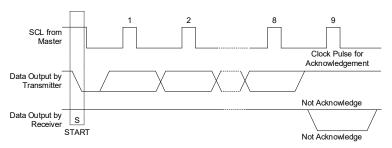

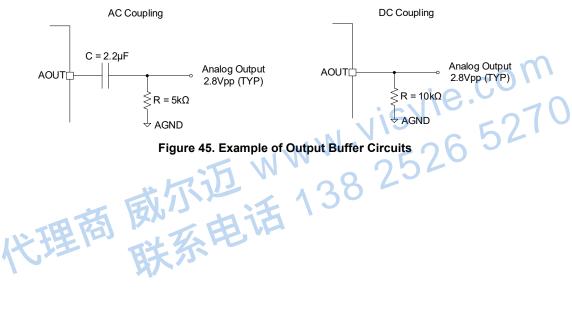

|                                           | $I_{VREFH}$                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | f <sub>S</sub> = 48kHz, 96kHz, 192kHz |     | 2.5  |     |       |